# GOVERNMENT OF TAMILNADU DIRECTORATE OF TECHNICAL EDUCATION CHENNAI – 600 025

# STATE PROJECT COORDINATION UNIT

# **Diploma in Electronics and Communication Engineering**

#### Course Code: 1040

# M – Scheme

# e-TEXTBOOK on TEST ENGINEERING for VI Semester DECE

# **Convener for ECE Discipline:**

Dr.M.JeganMohan M.E., MBA., Ph.D., (Management), Ph.D., (Engg)., M.I.S.T.E., Principal, 138. Government Polytechnic College

138, Government Polytechnic College, Uthappanaickanoor, Usilampatti, Madurai – 625 537.

# Team Members for Industrial Electronics: SCOM

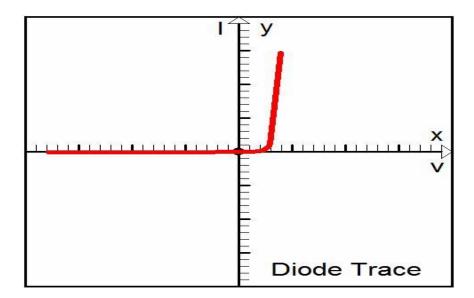

# Mr.G.ATHIRAJAN, B.E., M.E.,

HOD / ECE, K.L.Nagaswamy Memorial Polytechnic College, Madurai – 625 009.

# Mrs.G.Vijayakumari,

Lecturer /ECE , Government Polytechnic College, Melur – 625001.

# Validated By

#### Dr.Mrs.D.Selvathi,

Professor/ECE, 4960,Mepco Schlenk Engineering College, Virudhunagar – 626 005.

# GOVERNMENT OF TAMILNADU DIRECTORATE OF TECHNICAL EDUCATION CHENNAI – 600 025

# STATE PROJECT COORDINATION UNIT

# **Diploma in Electronics and Communication Engineering**

#### Course Code: 1040

# M – Scheme

# e-TEXTBOOK on TEST ENGINEERING for VI Semester DECE

# **Convener for ECE Discipline:**

Dr.M.JeganMohan M.E., MBA., Ph.D., (Management), Ph.D., (Engg)., M.I.S.T.E., Principal, 138. Covernment Polytechnic College

138, Government Polytechnic College, Uthappanaickanoor, Usilampatti, Madurai – 625 537.

# Team Members for Industrial Electronics: SCOM

# Mr.G.ATHIRAJAN, B.E., M.E.,

HOD / ECE, K.L.Nagaswamy Memorial Polytechnic College, Madurai – 625 009.

# Mrs.G.Vijayakumari,

Lecturer /ECE , Government Polytechnic College, Melur – 625001.

# Validated By

#### Dr.Mrs.D.Selvathi,

Professor/ECE, 4960,Mepco Schlenk Engineering College, Virudhunagar – 626 005.

### Contents

#

Need and Importance of Test Engineering 1.10, Principles of Fundamental Testing Methods 11.15, Basic Principles of Memory Testing 16.20, PCB Track Short Testing Methods 20.25, Concepts of Trouble Shooting PCBs 26.30, Manual and Automated PCB Trouble Shooting Techniques 31.38

# Unit-II Automated Testing Methods and Technology .....

Introduction to Automated Test Techniques 2.10, Fundamental of Digital Logic Families 2.15, Concepts of Back -Driving /Node Forcing Technique and its International Defense Standard 2.20, Concepts of Digital Guarding 2.25, Auto Compensation 2.30, Clock Termination 2.38, Functional Test Methods 2.45, Functional Testing of Digital, Analog and Mixed Integrated Circuits 2.50, Different types of Memory Module Functional Test 2.55.

Unit-III VI Signature Testing Methods and Technology .....

Fundamental of Electrical Characteristics 3.30, Effects of Curve Trace 1.15, Characteristics of Passive and Active Components 1.20, Understanding Composite VI-Curve and it deviations 1.25, Component Identification Ageing Effects with VI Curve Trace 1.30, Input and Output Characteristics of Digital Integrated Circuits 1.38, Good Versus Suspect interpretation Comparison 1.45

# Unit-IV Boundary Scan Testing Methods and Technology

Introduction to Boundary Scan 1.10, Need of Boundary Scan Test Technique 1.15, Principle of Boundary Scan Test 1.38, Boundary Scan Architecture 1.45, Application of Boundary Scan Test 1.55, Boundary Scan Standards 1.23, Boundary Scan Description Language (BSDL) 1.23, Interconnect Test 1.33, Serial Vector Format (SVF) Test 1.22, Basic of JTAG Port 1.23, Digital Integrated Circuit Test Using Boundary Scan Techniques 1.22.

# Unit-V ATE Test Program Generation and Semiconductor Testing

ATE in PCB Test 5.10, Test Fixtures 5.23, Basic of Automatic Test Program Generation 5.55, Standard Test Data Format STDF 5.55, Basic of Digital Simulator 5.22, Introduction to Semiconductor Test 5.66, Use of Load Boards 5.44.

Contents

| UNIT – I<br>INTRODUCTION TO TEST ENGINEERING                    | 8-33     |

|-----------------------------------------------------------------|----------|

| UNIT – II<br>AUTOMATED TESTING METHODS AND<br>TECHNOLOGY        | 38-69    |

| UNIT – III<br>V-I (Signature) TESTING METHODS AND<br>TECHNOLOGY | 72-87    |

| UNIT – IV<br>BOUNDARY SCAN TESTING METHODS<br>AND TECHNOLOGY    | 101- 109 |

UNIT – V ATE TEST PROGRAM GENERATION AND SEMICONDUCTOR TESTING 114-151 WWW.DINIS.COM

# Unit-1Introduction To Test Engineering

| S.NO | CONTENTS                                              | PAGE.NO |

|------|-------------------------------------------------------|---------|

| 1.1  | Need and Importance of Test Engineering               | 8       |

| 1.2  | Principles of Fundamental Testing Methods             | 15      |

| 1.3  | Basic Principles of Memory Testing                    | 17      |

| 1.4  | PCB Track Short Testing Methods                       |         |

| 1.5  | Concepts of Trouble Shooting PCBs                     | 21      |

| 1.6. | Manual and Automated PCB Trouble Shooting Techniques. | 33      |

|      |                                                       |         |

# UNIT – HAUTOMATED TESTING METHODS AND TECHNOLOGY

| S.NO   | CONTENTS                                       | PAGE. |

|--------|------------------------------------------------|-------|

|        |                                                | NO    |

| 2.1.1  | Introduction to Automated Test Techniques      | 38    |

|        | In-circuit Functional Test ICFT                |       |

| 2.1.2. | Models                                         | 42    |

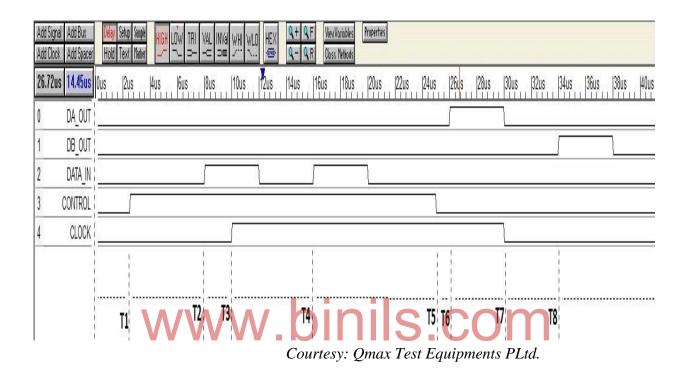

| 2.1.3  | TESTVECTOR                                     | 45    |

| 2.1.4  | Special considerations:                        | 48    |

| 2.1    | Board Testing                                  | 53    |

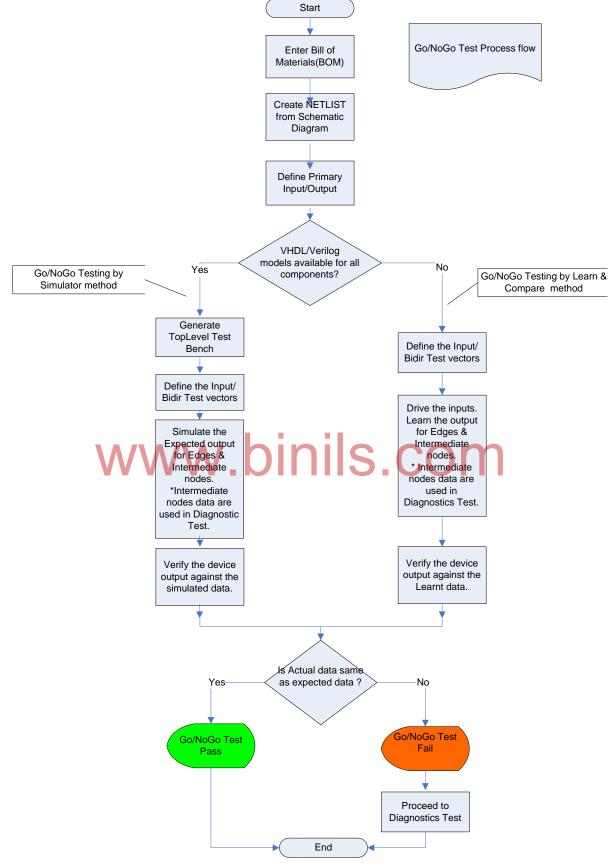

| 2.2.1  | Bill of Materials(BOM) Schematic diagram       | 54    |

| 2.2.2  | NET LIST                                       | 58    |

| 2.2.4  | Primary I/O                                    | 62    |

| 2.2.5  | Fixture Definition                             | 62    |

| 2.2.6  | Cluster Definition                             | 62    |

| 2.2.7  | Simulated output/Learnt Data.                  | 65    |

| 2.2.8  | Simulated output/Learnt Data                   | 68    |

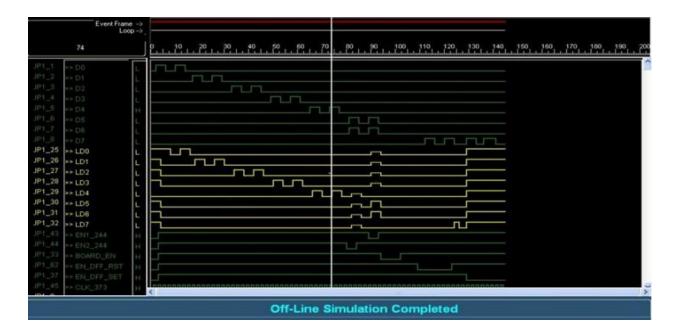

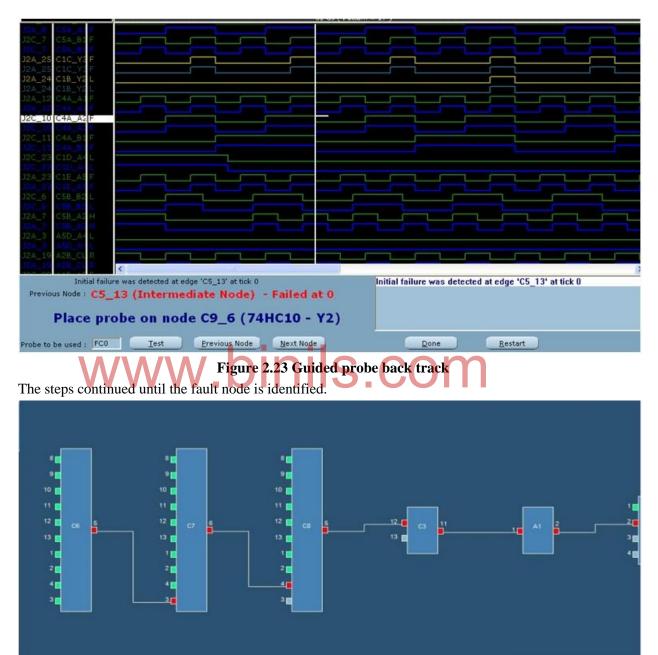

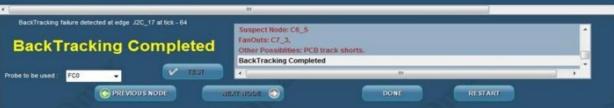

| 2.2.9  | Diagnostic Testing/Guided Probe Back Tracking: | 69    |

# UNIT – III V-I (Signature) TESTING METHODS AND TECHNOLOGY

| S.NO | CONTENTS                                                  | PAGE. |

|------|-----------------------------------------------------------|-------|

|      |                                                           | NO    |

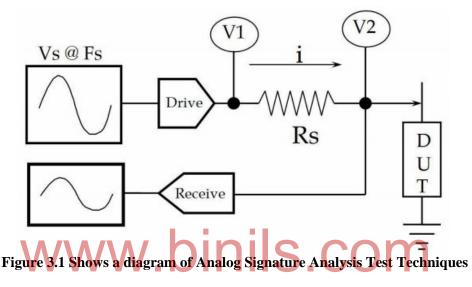

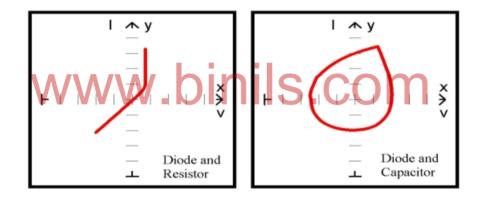

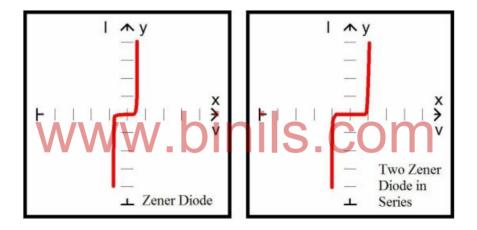

| 3.1  | Theory of Operations                                      | 72    |

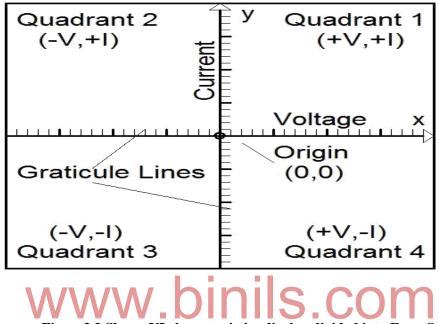

| 3.2  | VI Characteristics Display                                | 72    |

| 3.3  | VI - Effective Test System                                | 73    |

| 3.4  | Fundamental of Electrical Characteristics                 | 74    |

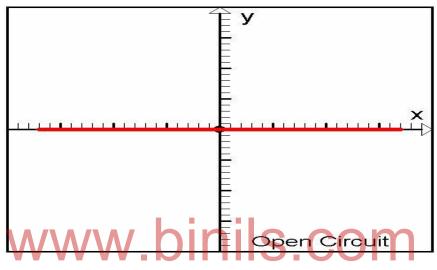

| 3.5  | Open Circuit Trace:-                                      | 74    |

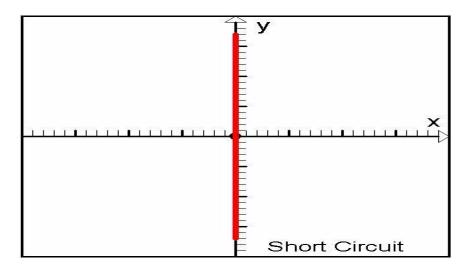

| 3.6  | Short Circuit Trace:-                                     | 75    |

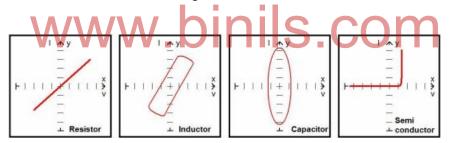

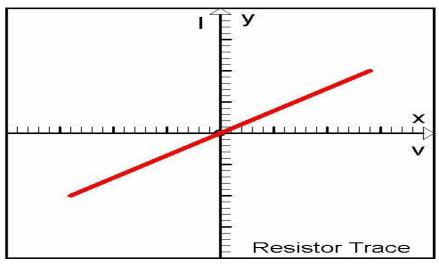

| 3.7  | Resistor Trace                                            | 76    |

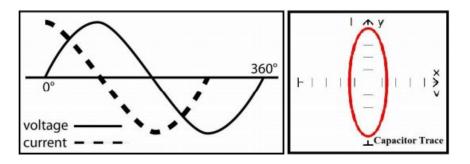

| 3.8  | Capacitor Trace                                           | 77    |

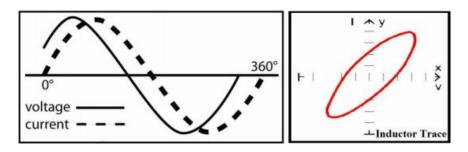

| 3.9  | Inductor Trace                                            | 78    |

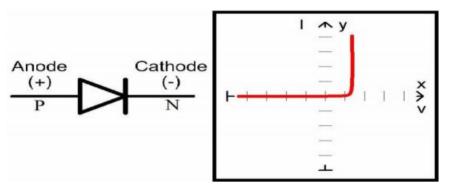

| 3.10 | Semiconductor Trace                                       | 78    |

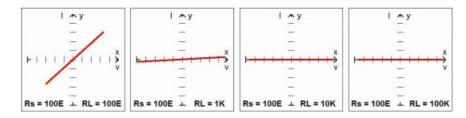

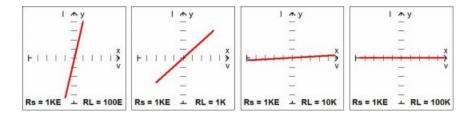

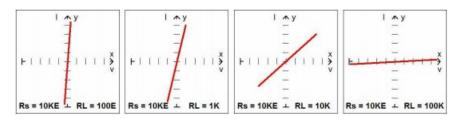

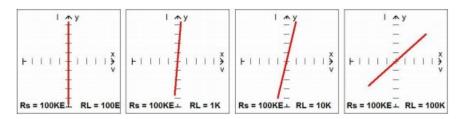

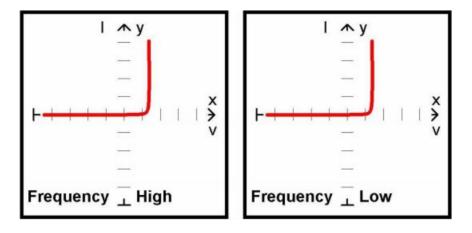

| 3.11 | Effect of Curve Trace                                     | 79    |

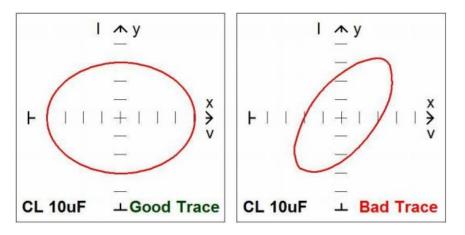

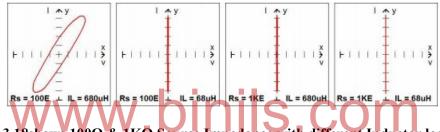

| 3.12 | Difference due to Capacitor Charge/Discharge:             | 80    |

| 3.13 | Resistor VI Characteristics:                              | 81    |

| 3.14 | Capacitor VI Characteristics:                             | 83    |

| 3.15 | Inductors VI Characteristics:                             | 86    |

| 3.16 | Effects of changing range voltage on inductive signatures | 87    |

# UNIT - IV WW DINIS COM BOUNDARY SCAN TESTING METHODS AND TECHNOLOGY

| CONTENTS                                                  | PAGE.                                                                                                                                    |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|                                                           | NO                                                                                                                                       |

| Boundary SCAN Theory of Operation                         | 101                                                                                                                                      |

|                                                           | 101                                                                                                                                      |

| 9Boundary Scan Cell                                       |                                                                                                                                          |

|                                                           | 104                                                                                                                                      |

| Boundary Scan Instructions                                |                                                                                                                                          |

| Boundary Scan Test applications                           | 106                                                                                                                                      |

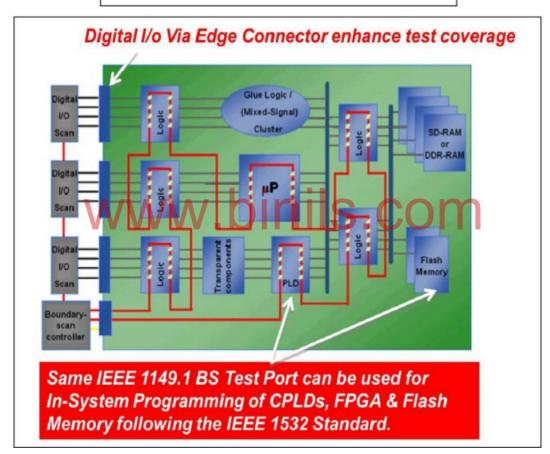

| Digital Input Output Edge Connector Enhance Test Coverage | 109                                                                                                                                      |

| _                                                         | Boundary SCAN Theory of Operation         9Boundary Scan Cell         Boundary Scan Instructions         Boundary Scan Test applications |

# **UNIT – VATE Test Program generation And Semiconductor testing**

| S.NO | CONTENTS                                                  | PAGE.<br>NO |

|------|-----------------------------------------------------------|-------------|

| 5.1  | ATE System for BOARD test                                 | 114         |

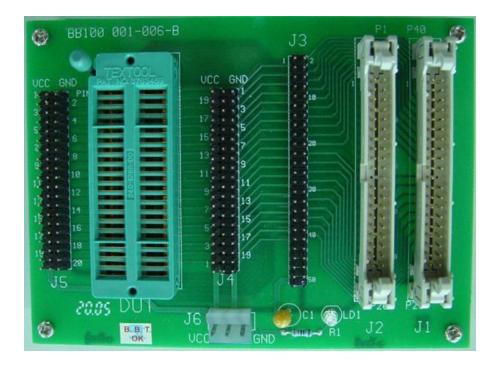

| 5.2  | Test Fixtures Basics of Automatic Test Program Generation | 122         |

| 5.3  | Basics of Automatic Test Program Generation               | 139         |

| 5.4  | Standard Test Data Format STDF                            | 146         |

| 5.5  | Basic of Digital Simulator                                | 151         |

# www.binils.com

#### Unit-I

#### INTRODUCTION TO TEST ENGINEERING

Test Engineering is a quality assurance testing, problem solving, where an test engineer will perform testing on devices or products. The role of test engineer is to test and deploy effective test solutions. Test Solutions for Aelectronics equipment, electronics components, software, automated devices, and other products, to ensure that they handle potential duress caused by typical usage, as well as to ensure that there are no flaws, bugs or errors hampering them.

A test engineer is required to full fill the product or system testing to ensure its functionality to meet the needs.

A test engineer is responsible for not only testing the quality of a product, but also must devise and develop tests that will assess the reliability of the product.

#### How to teach the concepts of such an important subject like Test engineering most effectively?

If students wants to gain a good understanding of "**Test Engineering**", Should understand the concepts of Test Engineering and test them independently.

For this one should acquire a practical knowledge of the Characteristics and Functions of different devices and components, and the various circuits.

Let us try to learn such skills by the proven scheme of "LEARNING BY DOING" Learning by doing an old Chinese proverb says

> I READ – I FORGET I SEE – I REMEMBER I DO – I UNDERSTAND

That is the way the "**TEST ENGINEERING**" theory and practical will guide to make learn and to understand the concepts of Test Engineering.

#### **1.1 Need and Importance of Test Engineering**

Test Engineering is not a new concept in the testing world. In earlier 90's there was no competition for development and to release a new product, so they have enough time line to test and validate a product before release, the product was reliable and precise.

In modern technology world, time to market and high quality has become huge headaches for companies, due to increased competition and complexity.

Several times we have seen in day to day life the product that we purchase those gets repair during the product's warranty period itself even immediately after purchase.

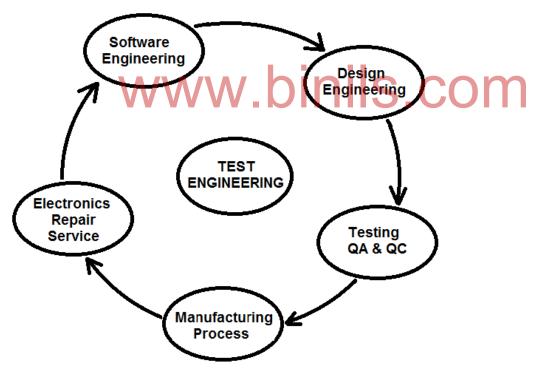

Best Example is Cell/Mobile Phone – Touch Not Working, Display Not Working, Heating Abnormal, No Sound, Network Issues etc. Figure 1.1 Shows the Test Engineering involved in various fields.

To over come those issues and to maintain the standard and quality of product, from product development till production cycle, companies had understand the importance and need of test engineering in modern world, to keep their market intact.

Overall, this drives manufacturing reliability and quality at the end of the line making sure that all units shipped out to customers are well tested, stressed, filtered out of any errors, and configured properly.

Work description of a test engineer varies based on the type of product they are testing, and what they purpose of the testing isFor example, the work description of a test engineer who works in software will vary from a test engineer that works in electronics.

Test engineers can have different expertise which depends on what test process they are more familiar with, figure shows test engineering involved in the various fields. In below figure 1.1 Shows the Test Engineering involved in various fields.

Figure 1.1 Shows the Test Engineering involved in various fields.

- Software Engineering

- Design Engineering

- Testing, Quality Control and Quality Assurances

- Manufacturing Process

- Electronics Repair Services

#### Software Engineering:-

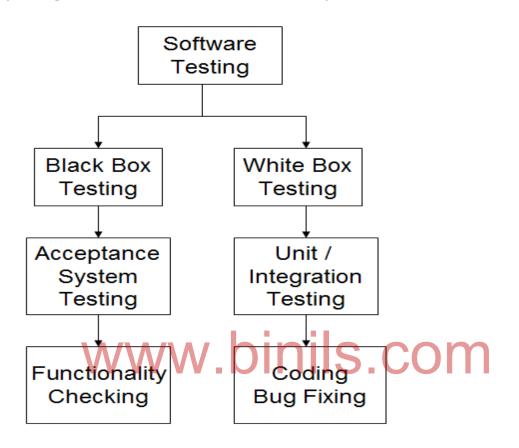

In Software Engineering (SWE) Software testing is a process of executing a program or application with the intent of finding the software bugs. The universe of testing automation can be neatly split into two predominant testing techniques known as black-box and white-box testing.

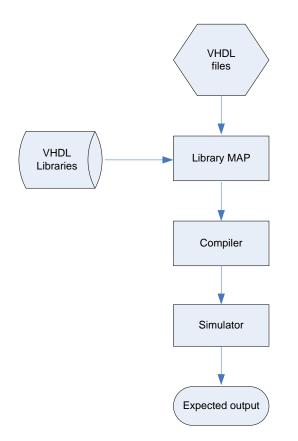

Figure 1.2 Shows the Software testing flow.

Other test design techniques exist, including gray-box testing, which is a combination of the previous two, however black-box and white-box testing approaches are the most widespread.Figure1.2 Shows the Software testing flow. Show in the figure 1.2 Shows the Software testing flow.

Black box testing is the method which is used to test the software without knowing the internal structure of code or program.

White box testing is a testing technique, which examines the program structure and derives test data from the program code.

| Criteria   | Black Box Testing        | White Box Testing          |

|------------|--------------------------|----------------------------|

|            | Black Box Testing is a   | White Box Testing is a     |

|            | software testing method  | software testing method in |

| Definition | in which the internal    | which the internal         |

| Definition | structure/ design/       | structure/ design/         |

|            | implementation of the    | implementation of the item |

|            | item being tested is not | being tested is known to   |

|                             | known to the tester                                                                         | the tester.                                                                               |

|-----------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Levels<br>Applicable to     | Mainly applicable to<br>higher levels of testing:<br>Acceptance Testing &<br>System Testing | Mainly applicable to lower<br>levels of testing:<br>Unit Testing & Integration<br>Testing |

| Responsibility              | Generally, independent<br>Software Testers                                                  | Generally, Software<br>Developers                                                         |

| Programming<br>Knowledge    | Not Required                                                                                | Required                                                                                  |

| Implementation<br>Knowledge | Not Required                                                                                | Required                                                                                  |

| Basis for Test<br>Cases     | Requirement<br>Specifications                                                               | Detail Design                                                                             |

Table 1.1 differentiates between Black Box & White Box Testing

For absolute newcomers, let us understand these three types of testing with an over simplified example in layman's terms:

For a functional mobile phone, the main parts required are "battery" and "SIM card - Subscriber identity module".

**Unit testing**: – the battery is checked for its life, capacity and other parameters. SIM card is checked for its activation.

Integration Testing: - battery and SIM card are integrated i.e. assembled in order to start the mobile phone.

**Functional Testing:** – the functionality of the mobile phone is checked in terms of its features and also battery usage as well as SIM card facilities.

The unit, Integration, and Functional testing: All three of them are correlated. To attain full coverage it is required to have unit tests for the paths/lines of code, functional and Integration tests for assurance that the 'units' work together cohesively.

#### **Design Engineering:-**

Test engineering place a major role in design engineering also know as hardware/embedded development design. Depending on the culture of the firm, in some of the firm/organization test engineer are involved in very earlier stages of the product design phase.

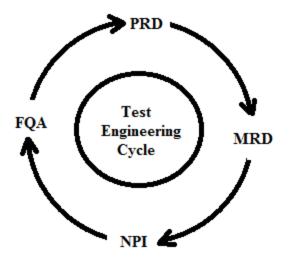

Figure 1.3 The Test Engineering Cycles / Process

Show in the figure 1.3 The Test Engineering Cycles / Process. The earlier stages could refer to Product Requirements Document (PRD) and Marketing Requirements Document (MRD), some of the earliest work done during a new product introduction (NPI). A test engineer ensures that a product is designed for both testability and manufacturability and to make sure standards are followed as per guideline.

- Product Requirements Document PRD

- Marketing Requirements Document MRD

- New Product Introduction NPI

- Final Quality Assurance FQA

S

COM

A Product Requirements Document (PRD) is a document containing all the requirements to a certain product. It is written to allow people to understand what a product should do. A PRD should, however, generally avoid anticipating or defining how the product will do it in order to later allow interface designers and engineers to use their expertise to provide the optimal solution to the requirements.

PRDs are most frequently written for software products, but can be used for any type of product and also for services. Typically, a PRD is created from a user's point-of-view by a user/client or a company's marketing department in the latter case it may also be called Marketing Requirements Document (MRD).

In business and engineering, new product development (NPD) is the complete process of bringing a new product to market.

A test engineer involve till the final quality audit (FQA) process, in the electronic hardware manufacturing world final quality audit process, is the last process flow before shipping a product. This process is established to ensure the unit has gone through and passed all the manufacturing or test process and is in good quality.

#### **Test Engineer Responsibility**

- Develop and document testing processes and procedures.

- Liaise with design engineers, product development teams and marketing personnel.

- Test technical and/or computer products and devices.

- Report problems or failures identified during testing.

- Make recommendations to product development team concerning improvements and solutions to problems.

# Some of the documents that the test engineers maintain or define:

- Test method.

- Diagnostic design specification.

- Manufacturing test requirement design specification.

- Design for testability (DFT).

- Design for manufacturability (DFM).

- Test plan.

# How Organizations are differ from with and without Test Engineer

Often organizations employ take shortcuts to be able to deliver final products. Because of these shortcuts, the product's manufacturability and testability becomes complicated (inability to read and write information, creating deviation from the process, etc.) which impacts the manufacturing complexity of a product.

Because of this complexity, bottlenecks in the manufacturing and delivery schedule delays are introduced. With this in mind, test engineers always get involved. Maintaining a Test Engineer in the firm is vital success of the product.

| Firm With Test Engineer      | Firm Without Test Engineer        |  |

|------------------------------|-----------------------------------|--|

| TE Develop proper test plans | No Proper Plans Executed          |  |

| TE Develops test cases       | Not a valid test case             |  |

| Ensure version management    | No Proper version maintained      |  |

| Maintain Quality of Product  | There is no product Stabilization |  |

| Timely Executions            | Time Delay                        |  |

| Cost Effective / Maintain    |                                   |  |

| Inventory                    | High Cost / Increased Inventory   |  |

| Maintain Standards           | Improper standard maintained      |  |

|                              | No such valid document            |  |

| All are documented           | maintained                        |  |

| No employ dependency         | Firm always depends on employ     |  |

Table 1.2shows what cause the firm with and without test engineer.

#### **Testing Quality Control and Quality Assurances**

Quality Control and Quality assurances are the part of Software and Hardware test engineering.

The testing world has a lot of terms for the activity that we undertake every day.You'll often hear the words QA, QC, and Test Engineering used interchangeably. While it is usually enough to get your point across with a developer, it is helpful to think about these terms and how they apply to the world of software testing.

In the classic definition QC is short for Quality Control, a process of verifying predefined requirements for quality. In the terms of an assembly-line this might involve pulling manufactured units off at the end of the process and verifying different parts of the assembly process.

For software the QC function may involve checking the software against a set of requirements and verifying that the software meets the predefined requirements.

Quality Assurance, on the other hand, is much more about providing the continuous and consistent improvement and maintenance of process that enables the QC job. We use the QC process to verify a product does what we think it does, and we use the QA process to give us confidence that the product will meet the needs of customers.

To that end the QA process can be considered a higher order level process that includes aspects of the QC process. It also goes beyond that to influence usability and design, to verify that functionality is not only correct, but useful.

| Quality Assurance                                       | Quality Control                                                      |

|---------------------------------------------------------|----------------------------------------------------------------------|

| It is a process which deliberate on providing assurance | QC is a process which deliberates on fulfilling the                  |

| that quality request will be achieved.                  | quality request.                                                     |

| A QA aim is to prevent the defect.                      | A QC aim is to identify and improve the defects.                     |

| QA is the technique of managing the quality.            | QC is method to verify the quality.                                  |

| QA does not involve executing the program.              | QC always involves executing the program.                            |

| All team members are responsible for QA.                | Testing team is responsible for QC.                                  |

| QA e.g. Verification.                                   | QC e.g. Validation.                                                  |

| QA means Planning for doing a process.                  | QC Means Action for executing the planned process.                   |

| Statistical Technique used on QA is known as            | Statistical Technique used on QC is known as                         |

| Statistical Process Control (SPC.)                      | Statistical Quality Control (SPC.)                                   |

| QA makes sure you are doing the right things.           | QC makes sure the results of what you've done are what you expected. |

| QA Defines standards and methodologies to followed in   | QC ensures that the standards are followed while                     |

| order to meet the customer requirements.                | working on the product.                                              |

| QA is the process to create the deliverables.           | QC is the process to verify that deliverables.                       |

#### **Quality Assurance vs Quality Control**

# Table 1.3 Quality Assurance vs Quality Control

#### **Manufacturing Process**

Test automation plays a major role in Semiconductor manufacturing process. Test automation refers to the automation of the process to test a product through the use of machines. Depending on the product, the machines that we are referring to could mean a combination of Automatic Test Equipment (ATE), handler, interface board, and test program that drives the ATE, as with the case of the IC chip testing. Test automation is a big part of test engineering. Further this topic will be discussed in unit -V elaborately.

#### **ERS – Electronics Repair Service**

Electronics repair service is also a one of the part of test engineering where engineers create, develop, install, maintain and trouble shoot electronics system and equipments using manual testing or by using automated testing as per the needs.

They are the ones usually operating and maintaining complex systems and equipments. Their expertise is invaluable in the fields of defense, aerospace, commercial electronics, medical technology and telecommunications among others.

# 1.2 Principles of Fundamental Testing Methods **SCOM**

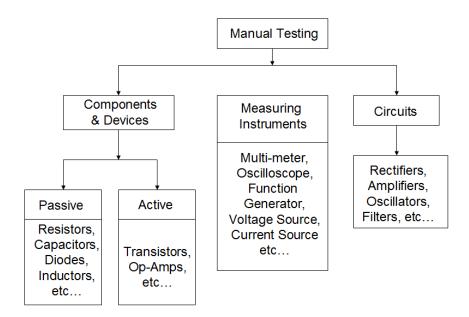

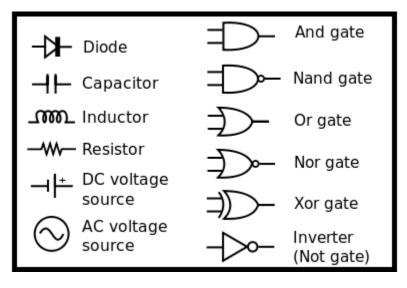

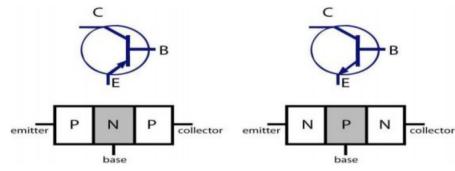

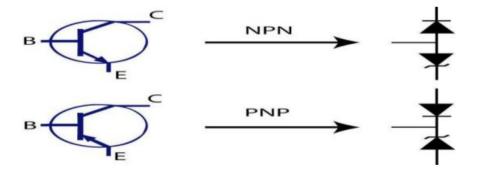

An electronic circuit consists of discrete and integrated semiconductor (semi-con) devices.

Discrete devices or discrete components denote passive components like Resistor, Capacitor, Inductor and active components like Diode, Transistor, FET, and LED etc.

Passive components do not require power supply and they often attenuate signals.

Active components amplify or process signal(s) and require power to operate.

Device testing can be done at two levels: functional and parametric.

A functional test determines whether or not the device works functionally for the intended use.

A parametric test measures all device parameters such as DC (Static) and AC (Dynamic) parameters to see if they meet the specified values. In the production of semiconductor devices, it is often the case that functional testing is done on all units while parametric testing is done on a small percentage of the units as test samples.

#### Manual Test verses Test Automation:-

Manual testing is the process where diagnostics are done with minimum measuring instruments with skilled trained test engineers. Manual testing is a good fit for smaller projects as well as companies without significant financial resources. Figure 1.3 Shows the Manual Testing using various Measuring Instruments

Figure 1.3 Shows the Manual Testing using various Measuring Instruments

The Above figure 1.3 is Show the Manual Testing using various Measuring Instruments Automated testing is the process through which automated tools run tests that repeat predefined actions, comparing a developing program's expected and actual outcomes.

# Testing can be done through both automated and manual testing, but which one you choose comes down to the associated costs and benefits of each on your particular project.

#### Automated vs. Manual Testing: The Pros and Cons of Each

#### **Automated Testing Pros:**

- Runs tests quickly and effectively.

- Can be cost effective in the long-term.

- Everyone can see results.

- Useful in Industrial, Telecommunications, Defense and in Manufacturing Sectors where large number of volumes are tested.

#### **Automated Testing Cons:**

- Tools can be expensive.

- Tools still take time, time goes into developing the automated tests and letting them run.

- Tools have limitations.

#### **Manual Testing Pros:**

- Short-term cost is lower.

- More likely to find real user issues.

- Manual testing is flexible.

• Useful in Commercial Testing with minimal instruments.

#### **Manual Testing Cons:**

- Certain tasks are difficult to do manually.

- Not stimulating.

- Can't reuse manual tests.

# 1.3 Basic Principles of Memory Testing

### **ROM and EPROM testing:**

ROM and EPROM testing is relatively easy. Since the contents are known in advance, all that the user has to do is to verify that all locations can be read from and that none of the original ROM content has changed. In principle, this can be done by manually stepping through each device location and comparing its content against the original documentation. In practice, this is impractical, and a more efficient strategy based on data compression is generally used. Using a data compression algorithm, the complete ROM content is reduced to single numerical value. This number is referred to as its "signature". Now, instead of having to cycle manually through the ROM to verify its content, we need only verify that its signature is correct.

To test using the signature verification method, a known good signature for each ROM is needed.

This is obtained by compressing the data from a known good ROM. These good signatures are then documented. During testing of a malfunctioning system, the signature for each suspect ROM is regenerated using the same procedure as was used to generate the original good signature. If the two signatures match, the ROM test passes.

In addition to checking ROM contents, this test inherently exercises all circuitry associated with ROM, including address and control lines, decoding circuitry, and the data bus interface. Thus a successful test not only verifies the ROM, it also verifies all its associated circuitry as well.

#### Generating a simple signature

The general method of generating a "good" signature is to compress the ROM contents into a checksum by summing its contents using an exclusive – OR summation. To generate such a checksum, start at the first location in ROM and successively add each word in turn until the complete ROM contents have been summed. Exclusive – OR addition is used instead of simple arithmetic addition, as it provides a higher level of uniqueness. This logic is used to generate the original "good" or "Gold" signature. The same algorithm is used in suspect system and the resulting signature is compared with "good" signature. The Simple checksum approach is not totally reliable. Although it detects all single – bit errors and many multiple errors, there are combinations of errors that it could miss. This method is useful for those in need of a quick and simple test.

An Improved version of the ROM test makes use of a Cyclic Redundancy Check (CRC) check character. This character is generated by a division process, rather than by the addition process described above. The CRC technique is inherently more reliable than the checksum technique and provides a much higher level of security.

CRC techniques are also used for signature analysis testing. In this case, however, data compression is usually performed by hardware rather than by software

#### **RAM testing**

RAM testing is basically to write a known test pattern in to the memory and read them back, report errors if a mismatch occurs. Comprehensive testing using all possible patterns would ensure that all patterns could be written to all locations and read back without affecting the contents of any other location. Such comprehensive testing is impractical, however, as it takes an enormous amount of time to test even moderate size memories. Instead, modern testing strategies use groups of tests, each concentrating on finding a subset of possible faults, but cannot guarantee 100 percent certainty.

Some common types of RAM tests are discussed below

#### Go-No Go Test

A fast way to test for gross failures is to write 0s to all locations, then read them back to ensure that no bits are stuck high, then write 1s to all locations, then read them back to verify that no bits are stuck low. It is used simply to verify the memory hardware interface.

#### Simple checkerboard Test:

Alternating 1s and 0s are written to memory in a checkerboard fashion, then read back and verified. The pattern is then inversed and the test is repeated. During the verification phase, exclusive-OR comparison of the patterns is used. This results in a bitmap in the accumulator showing the failing positions.

These tests check for hard errors plus failure of decode logic and other support circuits. They are sometimes used with a delay between memory fill and memory read to test for data retention. They do not catch many pattern-sensitive memory failures.

#### **Galloping Pattern Testing;**

To search for pattern sensitive and other soft errors, a group of "galloping patterns" test have been devised like "Walking 1s and 0s", "marching 1s and 0s" etc.

#### Simple march Test:

This test checks for address sensitivity as well as some cell interaction. Basically, it tests whether each location is capable of storing 1s and 0s and whether writing to any given location disturbs data residing at other locations. The program makes two passes through the RAM address range for each bit-thus, for an 8-bit processor, 2X8=16 passes are the required. Test patterns are produced by shifting a single logic 1 bit through the accumulator.

The first pass for each pattern stores the selected pattern in all locations; on the second pass for that pattern, each location is read and checked to see if anything has changed. If the data check is okay, the location is

marked to show that it has been tested. This is done by complementing its contents. If there is interaction between cells, it will be detected when the test reached the address affected.

#### **Random patterns:**

Random pattern testing is sometimes used to test for pattern sensitivity. In such a test, a series of pseudo random numbers is generated by software, written to memory, retrieved, and then checked for errors.

The process is repeated over and over in the hope that pattern sensitive errors will be uncovered.

These tests also verify not only the memory, but also all associated address bus, data bus, and decode and control logic associated with the sub system.

#### Length of Time to test:

Time limitations are an important factor in memory testing. For some schemes, testing time goes up proportional to the number of memory locations N to be tested (N test), while others go up proportional to the square of the number of locations to be tested (N^2) test. For very large memories, test duration using N^2 testing can take a long time.

#### **Functional Fault Models**

Classical fault models are not sufficient to represent all important failure modes in RAM. Sequential ATPG is not possible for RAM. Functional fault models are commonly used for memories: They define functional behavior of faulty memories. New fault models are being proposed to cover new defects and failures in modern memories:

#### **1.4 PCB Track Short Testing Methods**

Short circuit faults on PCBs are some of the very common but difficult problems faced in PCB production lines and PCB Repair centers. As the density of PC boards has increased, so have occurrences of shorts between traces. These shorts can result from manufacturing errors where the copper has not been properly etched away and from solder bridges when the boards are assembled. And most of the times, we know that there is a short circuit between two nodes or adjacent tracks in the PCB but do not know where this is exactly located in the PCB.

The problem now is to locate the bridge if it cannot be found simply with a magnifying glass. The short circuit locator allows us to do this, even if the short is hidden under an IC or other installed components.

Normally when using the multi-meters on the whole shorted track, it will show the same impedance. Because, conventional meters cannot distinguish the milli-ohm ranges. Using dedicated Short circuit locator instruments, we can measure the resistance in milli-ohms range.

#### **Concepts behind the Short Locator**

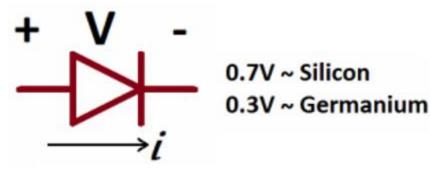

As we know diodes are made from semiconductor materials such as silicon or germanium. In order to "turn on" and conduct current in the forward direction, a diode requires a certain amount of positive voltage to be applied across it. The typical voltage required to turn the diode on is called the forward voltage (VF). Show in the figure 1.4 Silicon Diode approximately 0.7V Germanium 0.3V

Forward Voltages varies depend upon the semiconductor materials used for Silicon Diode approximately 0.7V and for Germanium based diode may be lower, around 0.3V. The type of diode also has some importance in defining the forward voltage drop; light-emitting diodes can have a much larger VF, while Schottky diodes are designed specifically to have a much lower-than-usual forward voltage.

Figure 1.4 Silicon Diode approximately 0.7V Germanium 0.3V

To detect shorts in the populated PCBs, the drive voltage from the short circuit locator equipment should be less than 200 mV. This is to avoid turning on the semiconductor devices inside the circuit, which could lead to misleading results.

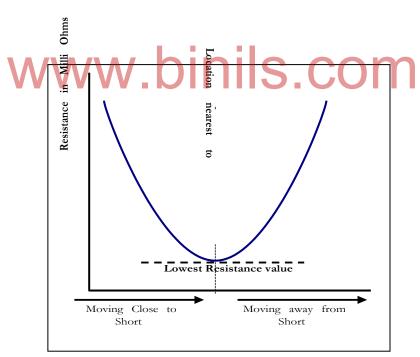

The concept is, the resistance will increase away from the short and it will decrease if it is towards the short. So the exact location of the short is where we get the lowest resistance value.

Short Locator is the exact tool that would be very useful to the technicians to pinpoint these faults. It overcomes the need to cut tracks and remove components trying to locate the fault. Before proceeding to understand the actual modes of operation, let us analyze the various reasons due to which the shorts occur in the tracks, components, etc.

#### **How Short Circuit Occurs**

Hair line and micro shorts: In highly dense PCBs it is possible that an illegal hair line has formed due to a manufacturing defect. Normally PCB

Manufacturers test them electrically with the use of expensive equipment to

Detect and reject such PCBs. But in small volume production of such PCBs it may not be cost effective in going for a electrical test and hence this defect may go unnoticed and trouble emerges when these PCBs are assembled and tested for its functionality

During Component assembly: While the components are assembled and soldered it is possible that a solder bridge between two adjacent component terminals is formed and causes short circuit.

Defective Components: Capacitors, especially tantalum types can get shorted internally and can cause Vcc-Gnd shorts. Semiconductors like diodes or transistors can get shorted fully or partially

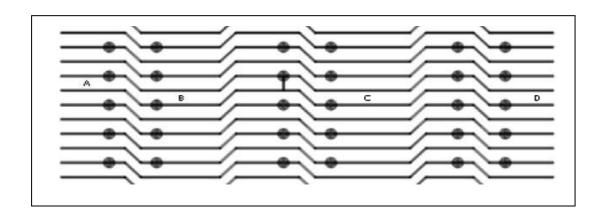

Ideally PCB tracks (electrical conductors) are supposed to have zero resistance, but in actual conditions they have small resistance. For a 15 mils track this could be in the range of 30 milliohms / inch, whereas for 8mils track this could be double. The exact location of the short is where the instrument reads the lowest value of resistance and this resistance could be detected with a sensitive instrument like dedicated short locator, even in power planes.

Short Locator can also be used in measuring the contact resistance of switches and relays in its milli-ohm mode. Shorts Locator is mainly used for detecting and locating short circuits in printed circuit boards (PCBs).

Using Multi-meter and other conventional troubleshooting tools, we can identify the shorts and opens in a circuit. But it may be difficult to identify the exact component responsible for the shorts, especially when the components are connected in parallel in the circuit. And, if a partial short occurs in a component /track, it is highly impossible to detect shorts using conventional tools.

So we have to go for advanced PCB troubleshooting tools such as Short circuit locators. With these tools and an understanding of the circuitry involved, the test engineer can pinpoint the cause of the fault with a high degree of certainty. And that is where dedicated short locator are used for accurately locating shorts between Vcc and Gnd, hairline shorts and also helps in isolating fan-out problems, etc. Needless to say, it pin points the shorted components or tracks.

# www.binils.com

#### 1.5 Concepts of Trouble Shooting PCBs

The PCBs are expected to give trouble free performance over their expected life duration. A factor like MTBF (mean time between failures) is calculated for a product based on the reliability factors of its constituents. This helps in planning a replacement or expected maintenance involving purchase of spares for the product.

The Mean time between failures (MTBF) is calculated as  $1/\lambda$ . where  $\lambda$  is the failure rate. Similarly, Mean time to repairs MTTR is calculated as  $1/\beta$  where  $\beta$  is the repair rate.

The fraction of time that a system is operating normally (i.e. failure free) is the system availability, which is given by

#### System availability=MTBF/(MTBF+MTTR)

Any Electronic system may fail in its useful lifetime and it is unpredictable. Unlike Mechanical systems, where one can examine tear and wear and estimate the life expectancy and periodic service requirements, in electronic systems no one can predict when a semiconductor will fail. It may work for its entire life cycle without failure OR it may fail within few hours of its operation.

Though no one can predict when the semi-con device will fail, certain things can be predicted over the age of the circuit boards, they are;

1) Electrolytic Capacitors drying out and changing values over aging.

- 2) Low quality connectors (not gold coated contacts) getting rusted and not making proper contacts.

- 3) PCBs without conformal coating and exposed to humidity / air with salt (near sea shores) can corrode and PCB tracks may get open circuited.

Though advances in Semiconductor technology and reliable manufacturing process have considerably reduced the failure rate, still there are failures in the field and it becomes necessary to understand their failure pattern and build expertise to isolate failing components and subsequent repair so that these can be maintained at minimal cost and in shortest possible time.

Repairing PCBs helps in many ways;

- 1) Low cost of maintenance, replacing entire PCB will cost multifold

- 2) No need to stock and maintain spare PCB inventory except for few vital ones

- 3) Reduces e-waste and saves environment

- 4) Generates employment and develop expertise

- 5) Generate feed back info on failure patterns and often failing components, which can help improve design and manufacturing technology for more reliable PCB production as well eliminate un-reliable components / suppliers.

Electronic Circuit Boards fail due to many factors both external and internal of the system. It may fail due to external factors such as erratic input power, faulty power supplies, Lighting, static discharge, Excess load or short circuits at output stage etc., The circuit may fail due to internal factor like a faulty resistor or capacitor or failed semi-con junction or an erratic function of an IC in the control circuit.

This first level of maintenance will be to isolate the faulty circuit card with a spare card so that the system can be up and running, the next step will be to get the circuit card repaired by using various trouble-shooting techniques so that exact failing component can be pin pointed and replaced to make the circuit card back to life. Electronic systems may range from simple gadgets to large systems running complex applications. Troubleshooting a large system involves considerable time and resources.

A logical approach to troubleshooting saves valuable time and waste of resources. With such a procedure we can trouble shoot any electronic equipment regardless of its complexity.

Let us discuss some steps involved in troubleshooting. A good understanding of these techniques is essential for a Test Engineer.

- 1. Symptom Recognition.

- 2. Symptom Elaboration.

- 3. Listing of probable faulty functions.

- 4. Localizing the Faulty function.

- 5. Localizing trouble to a circuit.

- 6. Replacing the faulty and verification.

- 7. Failure analysis

#### **Symptom Recognition**

A trouble symptom is an indication of some disorder or malfunction in an electronic equipment. Symptom recognition is the act of identifying such a sign when it appears. The knowledge of the normal equipment condition enables us to recognize an abnormal condition.

#### **Symptom Elaboration**

Symptom elaboration is the process of obtaining a more detailed description of the trouble symptom.

For example, consider a LCD Display. If its screen is not light, then recognizing that its screen is not lighted is not sufficient information to decide exactly what is causing the trouble but leads to look into the associated circuitry. The symptom may mean that the LCD display is burnt out or there is some disorder in the internal circuitry associated with display or intensity control is turned down too low or the power supply is not correct or even that the equipment is not turned on. Thus so many faults may cause a symptom like this.

In addition, manipulation of operating controls may have caused the damage to produce a symptom. Knowledge of the circuit changes that take place when we adjust a control will enable us to think ahead of each step and anticipate any damage that the action might produce.

Symptom elaboration cannot be accomplished unless the observed displays can be completely evaluated. The easier method for performing this evaluation is to have all the data handy for reference by recording the information as it is obtained. This will enable us to compare with information contained in the operating manual of that equipment. The data recording is an important tool in troubleshooting.

#### Listing of Probable faulty functions

This step applies to equipment that contains more than one functional area. It allows us to mentally select the function or functions that probably contain the malfunction as indicated by the information contained in the previous steps. This requires knowledge of the various functions of the equipment.

The functional block diagram helps us to arrive at the decision. The equipment functional block diagram is a symbolic representation of the functional units within the equipment as well as the signal flow paths between them. We can select a functional unit and ask the question whether fault in this functional unit could cause the original trouble symptom? If the answer is yes, then we ask the question, whether a fault in this functional unit produces the associated information obtained during symptom elaboration? If the answer is yes, we list this unit as probable faulty unit and go on to consider the details of this unit. If the answer is no, then we move to another unit.

#### Localizing the Faulty function

We may decide one or more functional units as the probable cause. We have to localize the faulty functional unit by systematically checking each probable functional unit finalized in the previous step.

The faulty functional unit may consist of many circuits. We have to conduct extensive testing to isolate the trouble to a specific circuit within the faulty functional unit.

#### **Bracketing Technique**

A technique called Bracketing technique is used to narrow down the trouble to a faulty circuit. This checking requires using the circuit diagram, which gives information about input and output of each functional block and the test point's. This diagram also gives the interconnecting cable details which will help us to conduct the checks.

#### Localizing the trouble to a circuit

When we place brackets either mentally or in the circuit, at the good input and at the bad output of the faulty function in the individual servicing block diagram, we know that the trouble exists somewhere between the brackets. The idea is to move the brackets one at a time and then make tests to determine whether the trouble is within the new bracketed area. We continue this process until the brackets isolate the defective circuit.

The most important factor in bracketing is determining where the brackets should be moved in this narrowing down process. The determination is made on the basis of

- > Our deductions form the analysis of systems and previous tests.

- > The type of circuit paths through which the signal flows.

- Accessibility of test point.

Now we have understood the signal paths that will help us to use the bracketing effectively.

There are 3 types of signal paths

- ▶ Linear path.

- > Branching path.

- Switching path.

**Linear Path:** The linear path is a series of circuits arranged so that the output of one circuit feeds the input of the following circuit. Thus the signal proceeds in a straight line through the circuit group without any return or branch paths.

**Branching Path:** The branching path may be either of two kinds: divergent or convergent. A divergent path is one in which two or more signal paths leave a circuit.

When two or more paths enter a circuit, the path is known as a convergent path.

**Switching Path:** The switching path contains a relay circuit that provides a different signal path for one or more given situations.

Tests are conducted in two modes:

- Signal tracing is accomplished by examining the signal at a test point with an oscilloscope, voltmeter or some other electronic test device.

- Signal injection is a method of applying an artificial signal to circuit to check its performance.

An example of the bracketing procedure can be shown by referring to following figure which represents a faulty functional unit. The Localizing the faulty function step, indicates a good input at test point A and a faulty output at test point E, indicating a trouble between these two test points.

#### Localizing the fault

Signal tracing would normally be used, since the signal at point A is known to be good. The signal at test point C is the first logical place to check, since this check will eliminate half of the circuit. The signal at test point C can be checked by placing a meter or scope at this point.

If the signal is satisfactory, the input bracket is moved from point A to point C. The next check at point D will then isolate the defective circuit. If the test is satisfactory, the trouble is in circuit 4& if the check is unsatisfactory, the trouble in circuit 3. Only the input bracket was moved.

If the check at point C is unsatisfactory, the output bracket is moved to this point. The next check at test point **B** will then isolate the defective circuit. If the signal is satisfactory, the trouble is in circuit **2**; if unsatisfactory, the trouble is in circuit **1**. In this case, only the output bracket was moved.

If signal injection is used, a test signal is injected at test point C and the output checked at test point E. If the results are satisfactory, the output bracket is moved to point C, and a signal is injected at test point B to isolate the defective circuit. If the signal is not correct at point E, the trouble is isolated between points C and E and the input bracket is moved to point C. Injecting a signal at point D will then isolate the defective stage.

### The half split method

The first method of bracketing to be considered will be the method for linear circuits. The best method of trouble shooting this type of circuit path is the half-split method.

Assume we have brackets at the input and output of a number of circuits in which the signal path through all circuits is linear. Unless the symptoms point to one circuit in particular that may be the trouble source, the most logical place to move a bracket is to a convenient test point near the center of the bracketed area. If a test indicates that the signal is good at this point, an input bracket should be left there. The brackets will then surround the second half of the linear circuit path, and the other half will be eliminated from the trouble area. If an incorrect signal is found at test point, an output bracket placed at this point will show that the trouble exists in the first half of the linear circuit path. This process should be repeated within the area now enclosed with brackets until the brackets surround only one circuit- the faulty circuit.

### **Branching Path method**

The first steps in the bracketing procedure for branching circuits should be isolating the trouble to one signal path.

The branching paths should be checked until the trouble is isolated to one of the signal paths. Then the half-split method may be applied to the faulty linear signal path.

#### Switching path method

The last type of signal path is the switching path. We have seen how electronic equipment are composed of various circuit chains interconnected to perform a desired task.

Control of these circuits along a switching branch, we initially test the final signal output for the branch following the switch or relay. When the switch or relay is a multiple contact type, each contact may be connected to a different circuit branch. In this case, it may be necessary to place the switch or cycle the relay to each position and check the final output of the branch associated with that position.

Once we have performed this test and isolated the trouble to one or more branches, we should check the suspected branches to locate the faulty branch. The next step is to apply the half–split or branching method, as required to isolate the faulty circuit.

In general, two or three or even all of the bracketing techniques may have to be used in combination, since most electronic equipment are complex enough to contain several circuit arrangements.

Each test should attempt to eliminate as many circuits from the bracketed area as possible, unless the symptoms indicate that one or more circuits are more likely to be at fault than the rest of the circuits. This process is continued until the brackets are at the input and output of single circuit.

#### **Component Failure Analysis**

This final step in the six-step troubleshooting procedure will require testing certain branches of the faulty circuit in order to determine where the faulty component lies. These branches are the interconnected networks associated with each element of the device in the faulty circuit.

A faulty component in one branch of a circuit can be caused by a faulty component in another branch or even in another circuit.

This step is designed to locate and verify all faulty components in the equipments being tested.

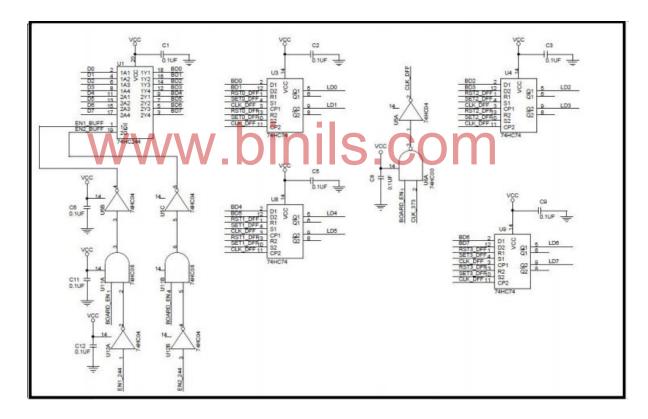

The schematic diagrams are helpful in this step. Schematic diagrams illustrate the detailed circuit arrangement of electronic component (represented symbolically) that make up the complete circuits within the equipment or functional unit. These diagrams show what is inside the blocks on an individual servicing block diagram and provide the final picture of electronic equipment.

# Types of circuit trouble WWDINIS.COM

The equipment failure can be classified into three types:

Complete failure of equipment will be obvious from the failure of function of the equipment

Degraded performance in which the normal symptoms will be available but the function will be below the expected levels. For example, the voltage output of a circuit may be 3 volts instead of expected 5 volts.

Intermittent failure refers to something that alternatively ceases and begins again. A component operates normally for a period of time, then fails completely or operates on a degraded level for a while, and then returns to normal operation. The cyclic nature of this malfunction is an aid in determining that it exists; however, it is often difficult to locate the actual faulted part.

#### **Review of the previous data**

A review of all the symptoms and test information obtained thus far will help to isolate other faulty components, whether the malfunction of these components is due to the isolated malfunction or some entirely unrelated cause. Suppose we have isolated a trouble to component and then discover that a failure of this

component would be not result in all the symptoms and irregularities in our test data. Then there is another defective component. When one component fails, it often results in abnormal voltages or currents that will cause damage to other components.

It is very important that isolating and replacing a malfunctioning component alone is not sufficient. We should analyze what is the cause for this malfunction. For example, we have isolated a particular transistor and found it to be burnt. In addition to replacing it, we should study what could have caused this transistor burnt. Then only, the trouble shooting will be complete. This also forms a feed back to the designer or manufacturing process in correction and in reliable equipment design.

#### Failure Types and Causes in the circuits

We have to be aware of the most important failure types and their causes in digital as well as analog circuits that can be troubleshoot using VI trace Technique. Three basic types of failure can be distinguished during the operation of digital circuits.

#### **Static Failures (Stuck-At Failures)**

These failures appear in the same manner, either during operation or testing, and are independent of the stimuli and their variations.

#### Breaks in Circuit Tracks (Stuck - At Open)

The absence of a necessary electrical contact causes a permanent fault.

### **Stuck At Short**

An unintentional short exists between one or more tracks and causes a permanent fault.

#### Stuck At High/ Stuck At Low faults

These permanent faults are also constant from when they first appear up to their removal and are independent of any simulation signals applied to the test object.

Two distinct cases exist: The potential at the faulty point in the circuit or connector pin remains either at the level of a logic high or logic low.

These are called Stuck at low or stuck at zero (S-A-0) for stuck to logic low, or stuck at high or stuck at One (S-A-1) for stuck to logic high.

The following possibilities can be taken into consideration for S-A-0 or S-A-1 Faults:

- Short circuit to ground for S-A-0 by either internal to the device or external by other components in the net.

- Short circuit to the supply rails for S-A-1 by either internal to the device or external by other components in the net.

#### **Dynamic Faults**

This category of faults is caused by components or circuit configurations which are used at the limits of their specifications, but which do not affect the function of the product at the time of testing. Again the following categories can be distinguished.

#### Supply failures;

The faults in the product are caused by excursions of the supply voltages outside their specified limits during operation. While testing with automatic testers, the voltage can temporarily assume the correct values. This leads to the conclusion the test object functions properly.

#### **Timing Faults**

A failure of the product is caused by faulty timing which falls outside the specified limits. This is especially important for synchronous circuits which are clocked (slow rise or fall times). Varying tolerances of devices lead to timing errors in synchronous circuits.

#### **Parametric Faults;**

In general, parametric errors appear when one or more parameters of a component or a circuit in normal operation fall outside their specified limits. These deviations are noticeable as faults if two components cannot work with each other. For example if the Input bias current of a device exceeds its specification, it will draw more current from the previous device, which may be in another circuit card and hence this type of fault is only discovered in normal operation and not during individual testing of circuit cards unless the equipment used to test the individual cards can check the parametric values of the edge devices. These type DC and AC parametric faults can cause trouble on system level test though individual circuit cards may be functional. DC Parametric Tests include Input Current, Output Fan out capability and Tri-State leakage currents. AC parametric Tests complicate the fault tracing considerably. Parametric faults can also be caused by environmental influences, such as temperature changes or erroneous adjustments of viable components. These faults are not very frequent.

#### **Intermittent Faults;**

Intermittent Faults appear only occasionally, either at regular intervals or sporadically and vanish again. This kind of fault is very difficult to recognize and locate. This type fault requires extravagant means of measurement (constant supervision and under certain circumstances, even special environmental conditions)

#### **Breaks in Circuit Connections;**

Breaks in circuit connections can occur because of thermal expansion, contraction orSpecial variable mechanical loading such as torsion, bending, or vibration

#### Short circuits

In a similar way to open connections, short circuits between neighboring tracks can or connectors can lead to intermittent faults because of changing conditions in the environment.

### **Exceeding Limits;**

Intermittent faults can also be caused by components which are used at the limits of their specifications.

#### **Bad Solder Joints;**

Dry or Cold solder joints can lead to intermittent faults

#### **Thermal and Electromagnetic Influences:**

A further cause for intermittent faults can be found in a short exposure to heat and electromagnetic radiation.

#### Fault types and fault Causes in Circuits during Manufacture

In addition to functional faults which can appear during normal operation, faults are known which occur during the manufacturing process. It is possible to distinguish between classes of faults as processing faults and population faults.

#### **Processing faults**

Processing faults manifest as breaks in copper tracks or as short circuits (caused by inadequate etching), or they lead to inadequate solder joints during the population process.

# **Population faults**

Population faults occur because of;

- Using wrong components

- Wrong orientation of correct components (diodes or integrated circuits)

- > Omission of components during the population procedures

- Using the correct components but with wrong values

Depending on a particular cause, manufacturing faults can, equally lead to static, dynamic or intermittent faults. This is especially true for bad components which are pushed to the limits of their specification or which are already defective.

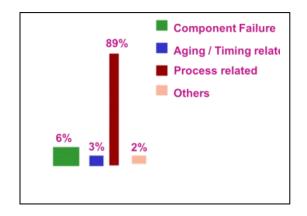

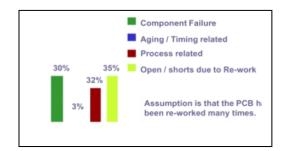

#### **Failure Frequencies**

The following table shows a characteristic example for the distribution of faults in the manufacture of building blocks. This is only an illustration and actual % will vary with assembly and manufacturing process and incoming QC of the components.

| Fault Type       | Fault Cause                                                                 | Distribution |

|------------------|-----------------------------------------------------------------------------|--------------|

| Population fault | <ul> <li>Missing components</li> <li>Components wrongly inserted</li> </ul> | 20%          |

|                     | <ul><li>Swapped components</li><li>Wrong component value</li></ul>                                                                                                  |     |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Manufacturing Fault | <ul> <li>Circuit track breaks and<br/>short circuits due to<br/>etching</li> <li>Open IC sockets</li> <li>Soldering fault</li> <li>Contaminated contacts</li> </ul> | 60% |

| Functional fault    | <ul> <li>Defective components<br/>(10%)</li> <li>Faulty interaction of<br/>components (10%)</li> </ul>                                                              | 20% |

# Table 1.4 distribution of faults in the manufacture of building blocks

Functional faults, which can appear during tests in manufacturing are mainly made up from the entries in the following table.

| Fault Type     | Fault Cause                      | Distribution |

|----------------|----------------------------------|--------------|

| Static faults  | Defective components             | 50%          |

|                | (predominantly -SA-1 and S-A-0)  |              |

| Dynamic faults | Timing faults (28%)              | 49%          |

|                | -One shots too long or too short |              |

|                | -Oscillatory output              |              |

|                | -Slow edges                      |              |

|                | Driver faults (21%)              | m            |

| Intermittent   | <b>N.DITII3.00</b>               | 10/          |

| faults         | Component at tolerance limits    | 1%           |

# **Table 1.4 Functional faults**

The following table shows some examples for typical failure rates of various components.

| Failure rate |  |

|--------------|--|

| (%)          |  |

| 3-10         |  |

| 1-5          |  |

| 0.75-2       |  |

| 0.2-1        |  |

|              |  |

| 0.1-1        |  |

| 0.05-1       |  |

|              |  |

# Table 1.5 fault types and troubleshooting methods

Thus we have seen in detail the fault types and troubleshooting methods in electronic circuits.

#### Manual and Automated PCB Trouble Shooting Techniques

### **Troubleshooting modes**

The manual troubleshooting can be classified as Online troubleshooting and Offline trouble shooting .

**Online trouble shooting** refers to trouble shooting with the board online – connected to the system. Normally using board extenders if the PCB is in a rack mounted. This means you are working with actual signals and working voltages. All safety considerations have to be taken care in this mode. You are supposed to have knowledge about the working of the board and its components. This mode can be useful when the cause of the trouble is known.

**Offline trouble shooting** refers to trouble shooting with the board taken out of the system. Now you have choice of feeding required signal at the required place and the function of the various stages of the board can be monitored using complex procedures.

The options include isolating/changing a suspected component. The basic factor of troubleshooting in minimum time and optimum use of tools/instruments to bring back a PCB online should be borne in mind.

The manual trouble shooting is limited to repairing board in small volumes as it is very difficult to isolate a device from the other devices and test all possible combinations for all the devices in the board. Also this demands skilled persons experienced in the particular board.

The time to find fault varies, depending on the complexity of the Circuit Card / Available documents / data sheets / experience and knowledge level of the test engineer and so on. This can be from few minutes to few hours to few days or even weeks. This is the greatest dis-advantage of manual trouble-shooting as even after spending a week, one may have to give up the trouble shooting if cannot find the faulty component.

When faced with a malfunctioning or inoperative system, the initial troubleshooting stage is very important. Since troubleshooting is both an art and a science, there is no single, unique way to go about any given problem. There is, however a general order of progression that makes sense to follow, as certain steps and procedures naturally follow after others. We should remember to always look at and correct obvious faults first.

#### **Guidelines for Troubleshooting**

An approach that has been found useful by the skilled test engineers for troubleshooting products in the general service environment is outlined below.

It recognizes that a large percentage of problems can be identified by visual inspection, probing and self test.

- 1. Perform a visual inspection

- 2. Reseat the boards and cables under the power off condition

- 3. Check the power supplies

- 4. Run the system self test if available. If the self test indicates the general area of fault, try "board swapping" if spare boards are available. If the fault cannot be localized using the self test, try minimizing the system, and if it works, build it up a little at a time until the fault re-appears.

- 5. When the problem is isolated to a particular board or section of a board, we should begin our investigation as follows;

#### Step1 Visual Inspection;

Check for blown fuses and replace if necessary Look improperly seated connectors, loose or broken wires, wrongly set switches, missing jumpers and so on.

Check for obviously damaged components (i.e. components burned or discolored due to overheating). Check both at the component and at the printed circuit board, since overheating is sometimes not visible on the components but shows up as brownish on the PC card instead.

#### **Step 2 Reseating Boards and components**

Edge connectors are a common source of problems. Power down the system and examine the edge connectors for contamination and clean them if necessary. Reseat any loose components (such as socketed ICs). Rest the board and power up.

#### **Step 3 Power supply Checks**

Check the power supply for missing voltages out of specifications. As voltage specifications are quite tight, logic supplies must be within +/- 5 percent (maximum tolerance limit) of supply voltage. We should remember that many systems use multiple supplies and all must be checked. Care should be taken to make such checks on the circuit boards at their points of usage, not just at the terminals of the power supplies. Because breaks can occur in interconnection paths due to loose or broken wires, poor solder joints, and so on. Checking the power supply quality for noise and ripple is also very essential.

#### **Step 4 Self-Testing**

The equipment may contain self-test routines that let the system test itself. Note however, that for these to be used; at least the main processor of the system must be functional and able to execute code.

ROM based self- test diagnostics. Routine may be supplied in ROM. These generally provide a quick check of ROM and RAM and a simple accessibility test of programmable switches and indicators are often used to involve test sequences and to display pass/fail results.

#### **Step 5-Board Swapping**

Board swapping involves the substitution of a known good board for a suspect one. If all the power supply voltages have been verified in a previous step, board swapping should be possible without a great deal of hazard to the good bard. Power should be removed before removing and inserting boards. When a faulty board has been identified, we still face the problem of how to find the actual part or component failure. The problem with board swapping as a service strategy leads to some other difficulties due to availability of good boards. Because removing a good board from the plant may affect the working environment.

#### **VLSI Component swapping:**

VLSI devices are very difficult to troubleshoot without advanced automated test equipment because of their complexity. In many systems, these devices are socketed for easy replacement. If so and if spare components are available, swapping VLSI devices in the suspect area can be done. It takes very little time to do this and can save a great deal of investigative time and effort. However, caution is required, as VLSI devices are very susceptible to damage from static electricity. Even if the device is not destroyed outright, static may cause problems that result in progressive degradation and ultimate failure, perhaps weeks or months in the future.

Swapping should therefore be done with a great deal of care and in a static -free environment. This should include a grounded, antistatic table mat and wrist strap, at the very least.

That's why we need Advanced Automated test equipment for troubleshooting where testing LSI and VLSI devices are possible in-circuit condition without removing or replacing it from the board.

#### **Gross Signal Checks**

Gross signal checks can be performed using a common oscilloscope. Checking for clocks, verifying logic levels, rise and fall times, and frequency according to data sheets for appropriate specifications. We must ensure that clock signals appear correctly on the buses, not just at the output of the clock circuits.

Oscilloscopes may also be used to investigate general system behavior. However, since they are inherently incapable of synchronizing to the complex signals present in systems, they cannot provide an accurate picture of such activity and are thus basically useful only for things that are periodic or obviously wrong.

Checking for the presence of signals on the various buses (address, data and control) and verify that they look reasonably correct that is, have signal activity on them if they should. (Some lines may not have activity on them because none is called for. For example, if the system ROM is located at the low end of memory and activity on high –order address lines even if there are no faults).

If general activity is present, check for the presence of decoded outputs, such as chip selectors, output enables and so on.

#### **1.6 Automated Troubleshooting Technologies**

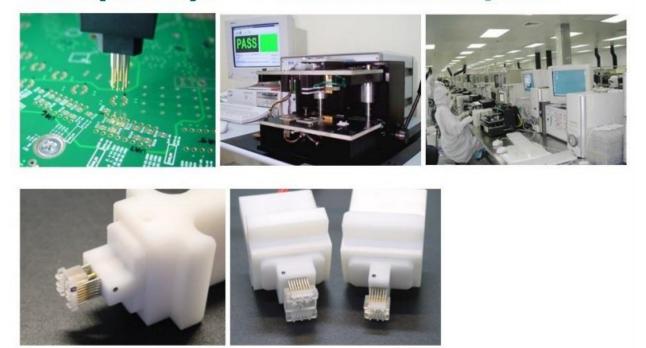

Automated Test Equipment (ATE) helps the test engineer to find faulty module of an electronic system through an automated testing process.

The main advantage of this automated test is that the predictable time determining if the module is good or bad (Go - No Go Test) and if the module is faulty, to detect a faulty component. This is unlike manual trouble-shooting which takes indefinite time and depends heavily on the skill set of the test engineer. It involves a systematic procedure and logical steps to identify a faulty component with speed and accuracy thereby saving time at a faction of replacement cost of the module.

In the production field, it is mostly preferred especially with medium to high volume production, since it provides an effective method of testing circuit boards at minimum cost and in shortest time.

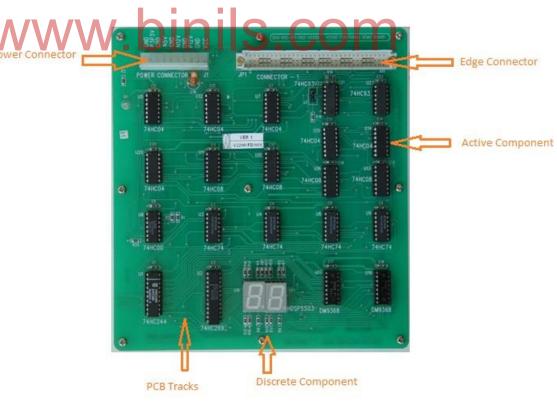

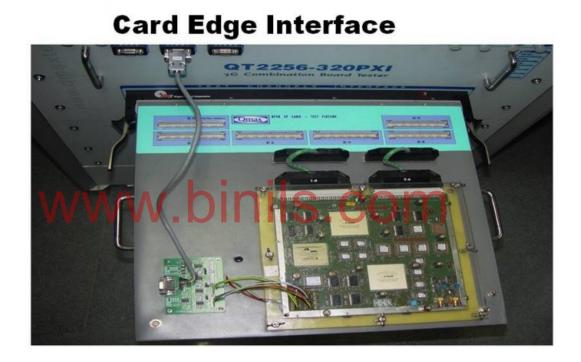

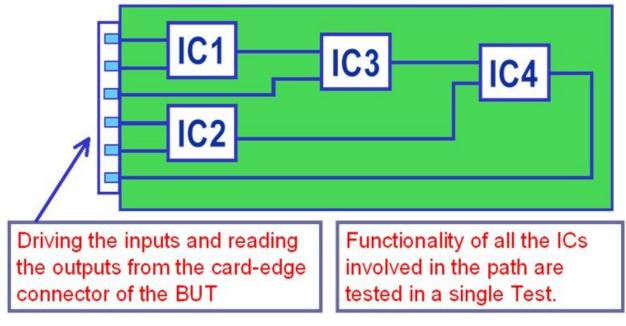

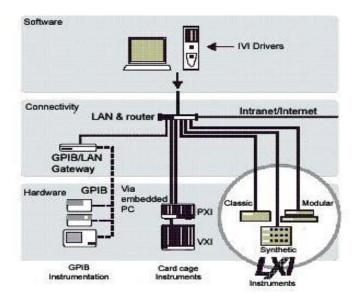

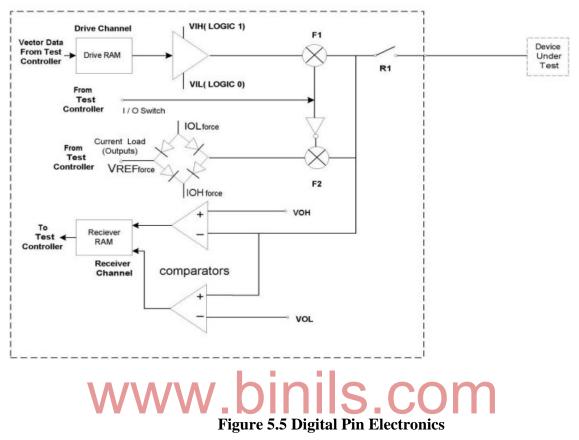

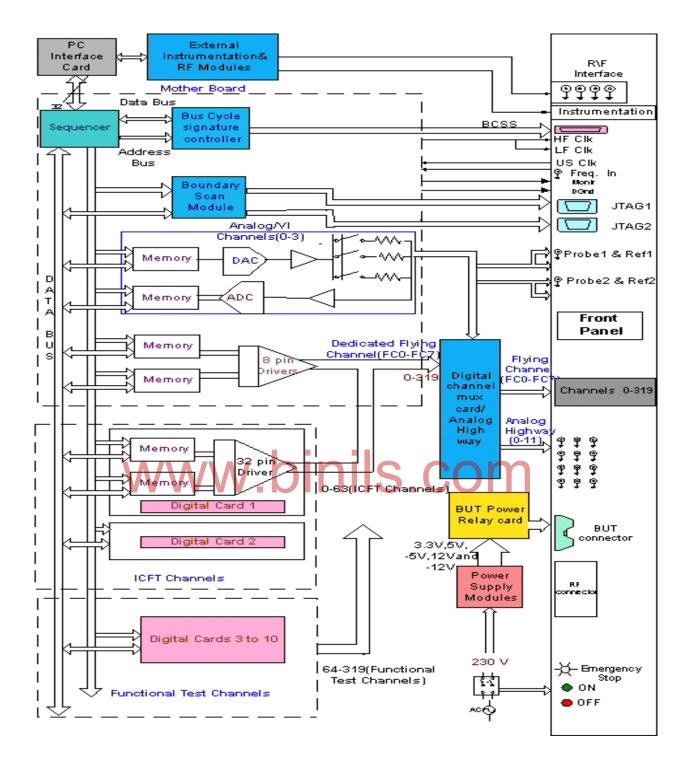

Basically an ATE system, which can be simply a tester used to test bare boards, components, or fully populated PCBs, comprises a computer-controlled test hardware with test instructions stored as software in the computer. The test pattern is applied to the board under test using test fixtures. This hardware interface, which can be either through Edge connectors, clips & probes or "bed of nails", provides an accurate low resistance contact to the circuit nodes of the board under test. The ATE will also have diagnostic facilities, embedded in the software, and usually a standard bus structure so that other COTS (commercially available off the shelf test system) can be interfaced through an analog highway switch matrix to carry out functional tests if required.

A variety of ATE systems at various levels of cost, complexity and diagnostic ability are available.

The different types are

- ➢ Component testers.

- ➢ Bare board testers.

- Manufacturing defect analyzers.

- ➢ In-Circuit Testers.

- ➢ Functional testers.

- ➢ Combinational testers.

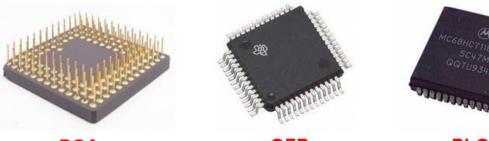

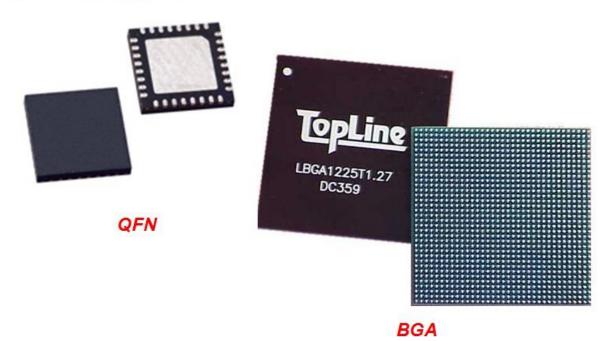

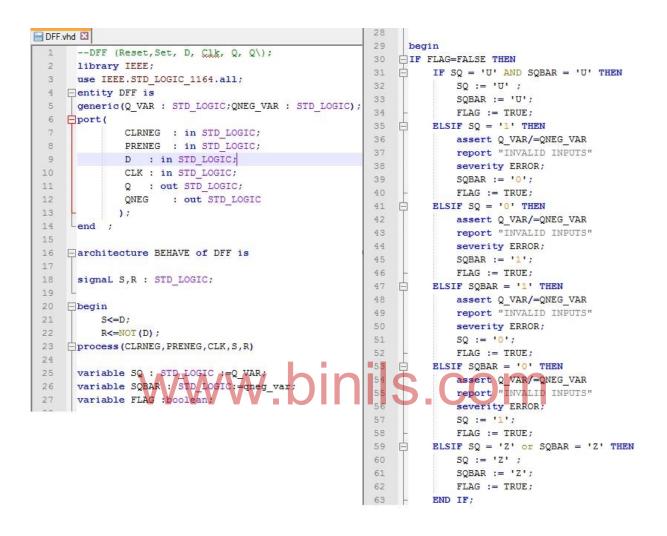

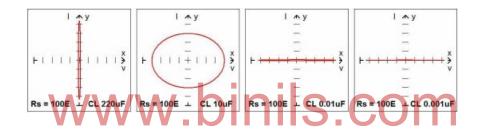

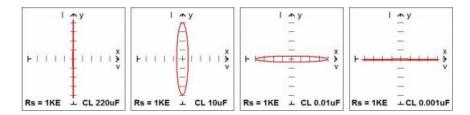

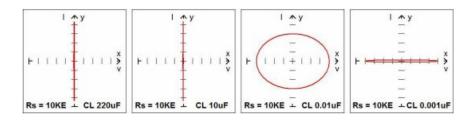

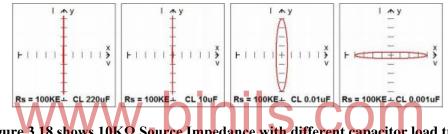

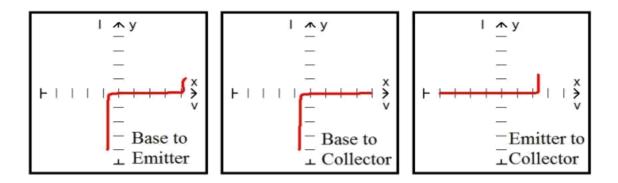

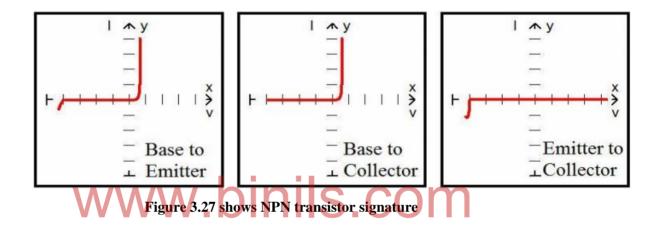

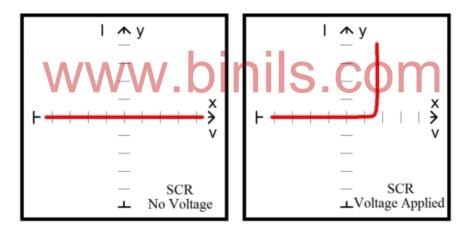

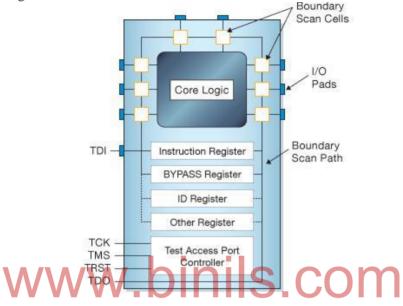

#### Component Testers;