www.binils.com for Anna University | Polytechnic and Schools

### 3.7 COMPARISON BETWEEN MICROPROCESSOR AND MICROCONTROLLER

| S.No | Microprocessor                                                              | Microcontroller                                                                                                                                    |

|------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | A microprocessor is a general                                               | A microcontroller is a dedicated chip                                                                                                              |

|      | purpose device which is called a                                            | which is also called single chip                                                                                                                   |

|      | CPU                                                                         | computer.                                                                                                                                          |

| 2    | A microprocessor do not contain<br>onchip I/OPorts, Timers,<br>Memories etc | A microcontroller includes RAM, ROM,<br>serial and parallel interface, timers,<br>interrupt<br>circuitry (in addition to CPU) in a single<br>chip. |

| 3    | Microprocessorsaremostcommonly used as theCPU inmicrocomputer systems       | Microcontrollers are used in small,<br>minimum component designs<br>performing control-oriented<br>applications.                                   |

| 4    | Microprocessor instructions are                                             | Microcontroller instructions are both bit                                                                                                          |

|      | mainly nibble or byte addressable                                           | addressable as well as byte addressable.                                                                                                           |

|      |                                                                             | IIC COM                                                                                                                                            |

| 5    | Microprocessor instruction sets                                             | Microcontrollers have instruction sets                                                                                                             |

|      | are mainly intended for catering                                            | catering to the control of inputs and                                                                                                              |

|      | to large volumes of data.                                                   | outputs.                                                                                                                                           |

| 6    | Microprocessor based system                                                 | Microcontroller based system design is                                                                                                             |

|      | design is complex and expensive                                             | rather simple and cost effective                                                                                                                   |

| 7    | The Instruction set of                                                      | The instruction set of a Microcontroller                                                                                                           |

|      | microprocessor is complex with                                              | is very simple with less number of                                                                                                                 |

|      | large number of instructions.                                               | instructions. For, ex: PIC                                                                                                                         |

|      |                                                                             | microcontrollers have only 35 instructions.                                                                                                        |

www.binils.com for Anna University | Polytechnic and Schools

| 8 | A microprocessor has zero | A microcontroller has no zero flag. |

|---|---------------------------|-------------------------------------|

|   | status flag               |                                     |

# www.binils.com

#### **3.6 INSTRUCTION SET**

The microcontroller 8051 instructions set includes 110 instructions, 49 of which are single byte instructions, 45 are two bytes instructions and 17 are three bytes instructions. The instructions format consists of a function mnemonic followed by destination and source field.

#### **ADDRESSING MODES OF 8051 :**

The way in which the data operands are accessed by different instructions is known as the addressing modes. There are various methods of denoting the data operands in the instruction. The 8051 microcontroller supports mainly 5 addressing modes. They are

- 1. Immediate addressing mode

- 2.Direct Addressing mode

- 3.Register addressing mode

- 4. Register Indirect addressing mode

- 5.Indexed addressing mode

# Immediate addressing mode :

The addressing mode in which the data operand is a constant and it is a part of the instruction itself is known as Immediate addressing mode. Normally the data must be preceded by a # sign. This addressing mode can be used to transfer the data into any of the registers including DPTR.

Ex: MOV A , # 27 H : The data (constant) 27 is moved to the accumulator registerADD R1 ,#45 H : Add the constant 45 to the contents of the accumulatorMOV DPTR ,# 8245H :Move the data 8245 into the data pointer register.

MOV P1,#21 H

# **Direct addressing mode:**

The addressing mode in which the data operand is in the RAM location (00 -7FH) and the address of the data operand is given in the instruction is known as Direct addressing mode. The direct addressing mode uses the lower 128 bytes of Internal RAM and the SFRs

MOV R1, 42H : Move the contents of RAM location 42 into R1 register

MOV 49H,A : Move the contents of the accumulator into the RAM location 49.

ADD A, 56H : Add the contents of the RAM location 56 to the accumulator

#### **Register addressing mode :**

The addressing mode in which the data operand to be manipulated lies in one of the registers is known as register addressing mode.

MOV A,R0 : Move the contents of the register R0 to the accumulator

ADD A,R6 :Add the contents of R6 register to the accumulator

MOV P1, R2: Move the contents of the R2 register into port 1

MOVR5, R2: This is invalid .The data transfer between the registers is not allowed.

# **Register Indirect addressing mode :**

The addressing mode in which a register is used as a pointer to the data memory block is known as Register indirect addressing mode.

MOV A,@ R0 :Move the contents of RAM location whose address is in R0 into A (accumulator)

MOV @ R1 , B : Move the contents of B into RAM location whose address is held by R1

When R0 and R1 are used as pointers, they must be preceded by @ sign,One of the advantages of register indirect addressing mode is that it makes accessing the data more dynamic than static as in the case of direct addressing mode.

# Indexed addressing mode :

This addressing mode is used in accessing the data elements of lookup table entries located in program ROM space of 8051.

Ex : MOVC A,@ A+DPTR

The 16-bit register DPTR and register A are used to form the address of the data element stored in on-chip ROM. Here C denotes code .In this instruction the contents of A are added to the 16-bit DPTR register to form the 16-bit address of the data operand.

# **INSTRUCTION SET OF 8051 MICROCONTROLLER**

All members of the 8051 family execute the same instructions set. The 8051 instructions set is optimized for 8-bit content application. The Intel 8051 has excellent and most powerful instructions set offers possibilities in control area, serial Input/Output, arithmetic, byte and bit manipulation.

It has 111 instructions they are

49 single byte instructions

- 45 two bytes instructions

- 17 three bytes instructions

The- instructions set is divided into four groups, they are

- Data transfer instructions

- Arithmetic instructions

- Logical instructions

- Call and Jump instructions

# DATA TRANSFER INSTRUCTIONS

This instruction copies the contents of the source location to the destination location. The contents of the source location are unchanged.

| Instruction   | Algorithm                                 | Example    | Functon                    |

|---------------|-------------------------------------------|------------|----------------------------|

| format        |                                           |            |                            |

| MOVA, Rn      | A = Rn                                    | MOV A, R1  | Move byte form register    |

|               |                                           |            | Rn to accumulator          |

| MOV A, direc  | $\mathbf{t} \mathbf{A} = \mathbf{direct}$ | MOV A,     | Move byte from direct      |

|               |                                           | 40H        | address to accumulator     |

| MOV A, @ R    | i A=[[Ri]]                                | MOVA,@     | Move the content of        |

|               |                                           | RO         | memory location to         |

|               |                                           |            | accumulator                |

| MOV A, #      | A = # data                                | MOV A, #31 | Move immediate             |

| data          |                                           | Н          | data to accumulator        |

| MOV Rn, A     | Rn = A                                    | MOV R5, A  | Move data from             |

|               |                                           |            | accumulator to register Rn |

| MOV Rn,       | Rn = direct                               | MOV R3,    | Move data from direct      |

| direct        |                                           | 30H        | address to register Rn.    |

| MOV Rn, #     | Rn = # data                               | MOV R7,    | Move immediate data to     |

| data          |                                           | #20H       | register Rn.               |

| MOV direct, A | direct =A                                 | MOV 80H,   | Move data from             |

|               |                                           | А          | accumulator to direct      |

|               |                                           |            | address                    |

| MOV direct,   | direct = Rn                               | MOV 30H,   | Move data from             |

| Rn            |                                           | R5         | register to direct         |

|               |                                           |            | address                    |

| MOV direct, | direct =   | MOV 20H, | Move data form source       |

|-------------|------------|----------|-----------------------------|

| direct      | direct     | 30H      | direct address to the       |

|             |            |          | destination direct address. |

| MOV direct, | direct =   | MOV 20H, | Move data from address      |

| @Ri         | [[Ri]]     | @R1      | specified in register Ri to |

|             |            |          | direct address.             |

| MOV direct, | direct =   | MOV 10H, | Move immediate data to      |

| #data       | #data      | #10H     | direct address              |

| MOV @Ri, A  | [[Ri]] = A | MOV @    | Move data form              |

|             |            | R0,A     | accumulator to memory       |

|             |            |          | location pointed by Ri      |

#### www.binils.com for Anna University | Polytechnic and Schools

#### **ARITHMETIC INSTRUCTIONS:**

|    | Mnemonic                    | Example    | Description                                  |

|----|-----------------------------|------------|----------------------------------------------|

|    | ADD A, Rn                   | ADD A, R0  | This instruction will add the byte in        |

|    |                             |            | register Rn of the selected register bank    |

|    |                             |            | with the byte in accumulator. The result     |

|    | $\Lambda \Lambda \Lambda I$ | V h        | is contained in the accumulator              |

| VI | ADD A, direct               | ADD A, 20H | This instruction will add the contents of    |

|    |                             |            | the memory location whose direct             |

|    |                             |            | address is specified in the instruction with |

|    |                             |            | the accumulator contents. The result of      |

|    |                             |            | addition will he stored in the               |

|    |                             |            | accumulator.                                 |

|    | ADD A, @ Ri                 |            | This instruction will add the contents of    |

|    |                             | R0         | memory location whose address is             |

|    |                             |            | pointed by register Ri of the selected       |

|    |                             |            | register bank with contents of the           |

|    |                             |            | accumulator. The result of addition is       |

|    |                             |            | stored in the accumulator                    |

|    | ADD A, # data               |            | This instruction will add the immediate 8    |

|    |                             | 30H        | bit data with data in the accumulator. The   |

|    |                             |            | result of addition is stored in the          |

|    |                             |            | accumulator.                                 |

| Mnemonics         | Addressing<br>mode      | Example         | Description                                                                                                                                                                                                                    |

|-------------------|-------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDC A, Rn        | Register<br>addressing  | ADDC A,<br>Rl   | This instruction will add the contents<br>of accumulator with the contents of<br>register Rn of the selected register<br>bank and carry flag. The result of<br>addition is stored in accumulator.                              |

| ADDC A,<br>direct | Direct<br>addressing    | ADDC A,<br>10H  | This instruction will add the contents<br>of memory location whose direct<br>address is specified in the instruction<br>with the contents of accumulator and<br>carry. The result of addition is stored in<br>the accumulator. |

| ADDC A,<br>@Ri    | Register<br>Indirect    | ADDC A,<br>@R0  | This instruction will add the contents<br>of memory location pointed by register<br>Ri of selected register bank with the<br>accumulator and earn' flag. The result<br>is stored in accumulator.                               |

| ADDC A,<br>#data  | Immediate<br>addressing | ADDC A,<br>#40H | This instruction will add the contents<br>of accumulator with immediate data<br>specified in the instruction along with<br>carry.                                                                                              |

| ADDC A, Rn        | Register<br>addressing  | ADDC A,<br>Rl   | This instruction will add the contents<br>of accumulator with the contents of<br>register Rn of the selected register<br>bank and carry flag. The result of<br>addition is stored in accumulator.                              |

| ADDC A, | Direct     | ADDC A, | This instruction will add the contents  |

|---------|------------|---------|-----------------------------------------|

| direct  | addressing | 10H     | of memory location whose direct         |

|         |            |         | address is specified in the instruction |

|         |            |         | with the contents of accumulator and    |

|         |            |         | carry. The result of addition is stored |

|         |            |         | in the accumulator.                     |

| ADDC A, | Register   | ADDC A, | This instruction will add the contents  |

| @Ri     | Indirect   | @R0     | of memory location pointed by           |

|         |            |         | register Ri of selected register bank   |

|         |            |         | with the accumulator and earn' flag.    |

|         |            |         | The result is stored in accumulator.    |

| ADDC A, | Immediate  | ADDC A, | This instruction will add the contents  |

| #data   | addressing | #40H    | of accumulator with immediate data      |

|         |            |         | specified in the instruction along with |

|         |            |         | carry.                                  |

#### www.binils.com for Anna University | Polytechnic and Schools

# LOGICAL INSTRUCTIONS:

| UGICAL INS  | TRUCTIONS          |           | - 11                                     |

|-------------|--------------------|-----------|------------------------------------------|

| Mnemonics   | Addressing<br>mode | Example   | Description                              |

| ANL A, Rn   | Register           | ANL A, R5 | This instruction will perform bit wise   |

|             | addressing         |           | logical AND operation between the        |

|             |                    |           | contents of accumulator and register     |

|             |                    |           | Rn of the selected register bank. The    |

|             |                    |           | result will be stored in the             |

|             |                    |           | accumulator                              |

| ANL A,      | Direct             | ANL A,    | This instruction will bit wise logically |

| direct      | addressing         | 70H       | AND the contents of accumulator with     |

|             | 6                  |           | the contents of memory location          |

|             |                    |           | whose direct address is specified in     |

|             |                    |           | the instruction. The result will be      |

|             |                    |           | stored in the accumulator                |

| ANL direct, | Direct             | AXL 30H,  | This instruction will bit wise logically |

| А           | addressing         | А         | AND the contents of memory location      |

|             |                    |           | whose direct address is specified in     |

|             |                    |           | the instruction with the contents of     |

|             |                    |           | accumulator. The result will be stored   |

|              |         |                                    |                     | in the memory location whose direct<br>address is specified in the instruction.                                                                                                                             |

|--------------|---------|------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANL .        | A, ®Ri  | Register<br>Indirect<br>Addressing | ANL A,<br>@R1       | This instruction will bit wise logically<br>AND the contents of accumulator with<br>the contents of memory location<br>pointed by register Ri of the selected<br>register bank. The result will be stored   |

| ANL<br>#data | А,      | Immediate<br>addressing            | ANL A,<br>#57H      | This instruction will bit wise logically<br>AND the contents of accumulator with<br>the immediate data specified in the<br>instruction. The result will be stored in<br>the accumulator.                    |

| ANL of #data | direct, | Immediate<br>addressing            | ANL<br>54H,<br>#33H | This instruction will bit wise logically<br>AND the contents of memory location<br>whose direct address is specified in the<br>instruction with the contents of with<br>the immediate data specified in the |

|              |         |                                    |                     | instruction. The result will be stored in<br>the memory location whose direct<br>address is specified in the instruction.                                                                                   |

#### CLRA

• This instruction will clear all the bits of accumulator to zero.

CPLA

• This instruction will complements all the bits (l's complement) of the accumulator.

# RLA

- This instruction will rotate the eight bits in the accumulator by one bit to the left.

- Addressing mode: Register Specific addressing mode.

RLCA

www.binils.com for Anna University | Polytechnic and Schools

- This instruction will rotate the eight bits in the accumulator and the carry flag together by one bit to the left

- Addressing mode: Register Specific addressing mode.

#### RRA

- This instruction will rotate the eight bits in the accumulator by one bit to the right.

- Addressing mode: Register Specific addressing mode.

#### RRCA

- This instruction will rotate the eight bits in the accumulator and the carry flag together by one bit to the right.

- Addressing mode: Register Specific addressing mode.

#### SWAP A

This instruction interchanges the low order and high order nibbles of the accumulator. Operation:

Addressing mode: Register Specific addressing mode.

# WWWDINGE Register Specific addressing mode.

# 3.1 FUNCTIONAL BUILDING BLOCKS & HARDWARE ARCHITECTURE Introduction :

A decade back the process and control operations were totally implemented by the Microprocessors only. But now a days the situation is totally changed and it is occupied by the new devices called Microcontroller. The development is so drastic that we can't find any electronic gadget without the use of a microcontroller. This microcontroller changed the embedded system design so simple and advanced that the embedded market has become one of the most sought after for not only entrepreneurs but for design engineers also.

#### Microcontroller

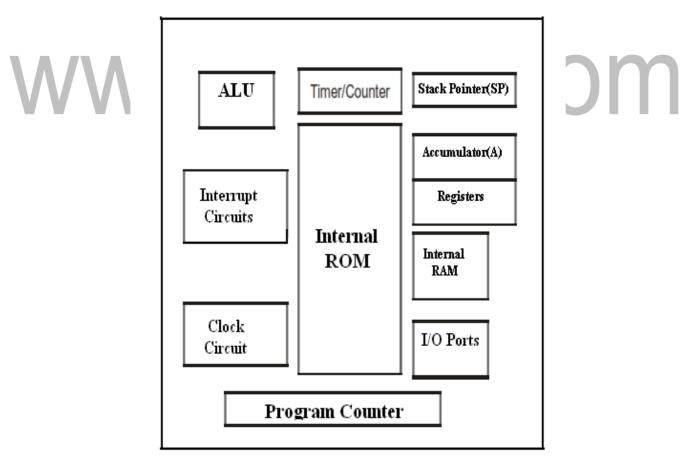

A single chip computer or A CPU with all the peripherals like RAM, ROM, I/O Ports, Timers, ADCs etc... on the same chip. For ex: Motorola's 6811, Intel's 8051, Zilog's Z8 and PIC 16X etc...

# Figure 3.1.1 Block Diagram of a Microcontroller

[Source: "Microprocessor Architecture Programming and Application" by R.S. Gaonkar, page-]

| S.No | Microprocessor                                                                                      | Microcontroller                                                                                                                                 |

|------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | A microprocessor is a general                                                                       | A microcontroller is a dedicated chip                                                                                                           |

|      | purpose device which is called<br>a CPU                                                             | which is also called single chip computer.                                                                                                      |

| 2    | A microprocessor do not<br>contain onchip I/Ports, Timers,<br>Memories etc                          | A microcontroller includes RAM,<br>ROM, serial and parallel interface,<br>timers, interrupt circuitry (in addition<br>to CPU) in a single chip. |

| 3    | Microprocessors are most<br>commonly used as the CPU in<br>microcomputer systems                    | Microcontrollers are used in small,<br>minimum component designs<br>performing control-oriented<br>applications.                                |

| 4    | Microprocessor instructions are<br>mainly nibble or byte<br>addressable                             |                                                                                                                                                 |

| 5    | Microprocessor instruction sets<br>are mainly intended for<br>catering to large volumes of<br>data. | Microcontrollers have instruction sets<br>catering to the control of inputs and<br>outputs.                                                     |

| 6    | Microprocessor based system<br>design is complex and<br>expensive                                   | Microcontroller based system design<br>is rather simple and cost effective                                                                      |

| 7    | The Instruction set of microprocessor is complex with large number of instructions.                 | The instruction set of a<br>Microcontroller is very simple with<br>less number of instructions. For, ex:                                        |

|   |                           | PIC microcontrollers have only 35   |

|---|---------------------------|-------------------------------------|

|   |                           | instructions.                       |

|   |                           |                                     |

| 8 | A microprocessor has zero | A microcontroller has no zero flag. |

|   | status flag               |                                     |

|   |                           |                                     |

#### **Evolution of Microcontrollers :**

The first microcontroller TMS1000 was introduced by Texas Instrumentsin the year 1974. In the year 1976, Motorola designed a Microprocessor chip called 6801 which replaced its earlier chip 6800 with certain add-on chips to make a computer. This paved the way for the new revolution in the history of chip design and gave birth to a new entity called "Microcontroller". Later the Intel company produced its first Microcontroller 8048 with a CPU and 1K bytes of EPROM, 64 Bytes of RAM an 8-Bit Timer and 27 I/O pins in 1976. Then followed the most popular controller 8051 in the year 1980 with 4K bytes of ROM,128 Bytes of RAM, a serial port, two 16-bit Timers, and 32 I/O pins. The 8051 family has many additions and improvements over the years and remains a most acclaimed tool for today's circuit designers. INTEL introduced a 16 bit microcontroller 8096 in the year 1982. Later INTEL introduced 80c196 series of 16bit Microcontrollers for mainly industrial applications. Microchip, another company has introduced an 8-bit Microcontroller PIC 16C64 in the year 1985. The 32-bit microcontrollers have been developed by IBM and Motorola. MPC 505 is a 32-bit RISC controller of Motorola. The 403 GA is a 32 -bit RISC embedded controller of IBM. In recent times ARM company (Advanced RISC machines) has developed and introduced 32 bit controllers for high-end application devices like mobiles, Ipods.

# **Microcontroller Development Tools:**

To develop an assembly language program we need certain program development tools. An assembly language program consists of Mnemonics which are nothing but short abbreviated English instructions given to the controller. The various development tools required for Microcontroller programming are explained below.

# 1. Editor :

An Editor is a program which allows us to create a file containing the assembly language statements for the program. Examples of some editors are PC write Wordstar.

As we type the program the editor stores the ACSII codes for the letters and numbers in successive RAM locations. If any typing mistake is done editor will alert us to correct it. If we leave out a program statement an editor will let you move everything down and insert a line. After typing all the program we have to save the program . This we call it as source file. The next step is to process the source file with an assembler.

#### Ex: Sample. asm

#### 2.Assembler :

An Assembler is used to translate the assembly language mnemonics into machine language( i.e binary codes). When you run the assembler it reads the source file of your program from where you have saved it. The assembler generates a filee with the extension .hex. This file consists of hexadecimal values encoding a sequence of data and their starting offset or absolute address.

**3.**Compiler : A compiler is a program which converts the high level language program like "C" into binary or machine code. Using high level languages it is easy to manage complex data structures which are often required for data manipulation. Because of its ease , flexibility and debug options now a days the compilers have become very popular in the market. Compilers like Keil ,Ride and IAR workbench are very popular.

#### 3. Debugger/Simulator :

A debugger is a program which allows execute the program, and troubleshoot or debug it. The debugger allows to look into the contents of registers and memory locations after the program runs. We can also change the contents of registers and memory locations and rerun the program. Some debuggers allows to stop the program after each instruction so that you can check or alter memory and register contents. This is called single step debug. A debugger also allows to set a breakpoint at any point in the program. If we insert a break point , the debugger will run the program up to the instruction where the breakpoint is put and then stop the execution.

A simulator is a software program which virtually executes the instructions similar to a microcontroller and shows the results. This will help in evaluating the results without committing any errors. By doing so we can detect the possible logic errors.

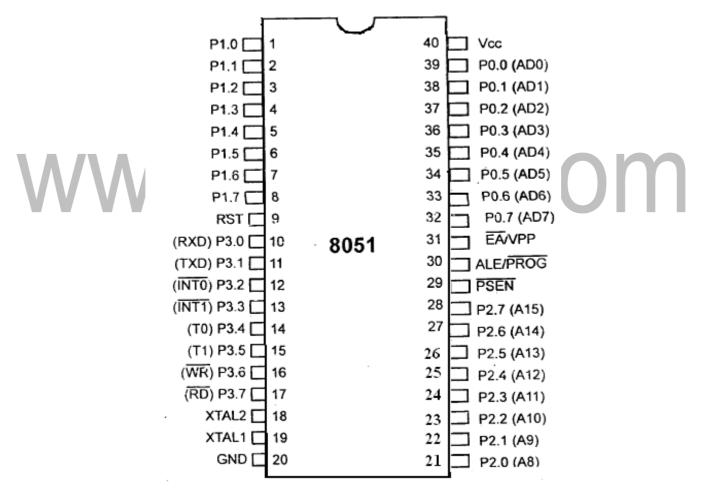

#### **INTEL 8051 Micrcontroller :**

The 8051 microcontroller is a very popular 8-bit microcontroller introduced by Intel in the year 1981 and it has become almost the academic standard now a days. The 8051 is based on an 8-bit CISC core with Harvard architecture. Its 8-bit architecture is optimized for control applications with extensive Boolean processing. It is available as a 40-pin DIP chip and works at +5 Volts DC. The salient features of 8051 controller are given below.

#### **Salient Features :**

The salient features of 8051 Microcontroller are

- i. 4 KB on chip program memory (ROM or EPROM)).

- ii. 128 bytes on chip data memory(RAM).

- iii. 8-bit data bus

- iv. 16-bit address bus

- v. 32 general purpose registers each of 8 bits

- vi. Two -16 bit timers T0 and T1

- vii. Five Interrupts (3 internal and 2 external).

ix. Four Parallel ports each of 8-bits (PORT0, PORT1, PORT2, PORT3) with a total of 32 I/O lines.

x. One 16-bit program counter and One 16-bit DPTR (data pointer)

xi. One 8-bit stack pointer

xii. One Microsecond instruction cycle with 12 MHz Crystal.

xiii. One full duplex serial communication port.

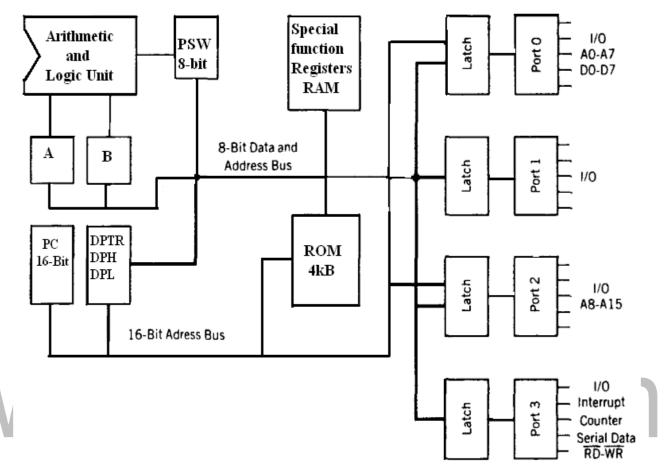

# Architecture & Block Diagram of 8051 Microcontroller:

The architecture of the 8051 microcontroller can be understood from the block diagram. It has Harward architecture with RISC (Reduced Instruction Set Computer) concept. The block diagram of 8051 microcontroller is shown in Fig 3. below1.It consists of an 8-bit ALU, one 8-bit PSW(Program Status Register), A and B registers , one 16-bit Program counter , one 16-bit Data pointer register(DPTR),128 bytes of RAM and 4kB of ROM and four parallel I/O ports each of 8-bit width. 8051 has 8-bit ALU which can perform all the 8-bit arithmetic and logical operations in one machine cycle. The ALU is associated with two registers A & B

#### A and B Registers:

The A and B registers are special function registers which hold the results of many arithmetic and logical operations of 8051. The A register is also called the Accumulator and as it's name suggests, is used as a general register to accumulate the results of a large number of instructions. By default it is used for all mathematical operations and also data transfer operations between CPU and any external memory.

Figure 3.1.2 Block Diagram of 8051 Microcontroller

[Source: "Microprocessor Architecture Programming and Application" by R.S. Gaonkar, page-]

#### The R registers:

The "R" registers are a set of eight registers that are named R0, R1, etc. up to and including R7. These registers are used as auxiliary registers in many operations. The "R" registers are also used to temporarily store values.

#### **Program Counter(PC):**

8051 has a 16-bit program counter. The program counter always points to the address of the next instruction to be executed. After execution of one instruction the program counter is incremented to point to the address of the next instruction to be

executed. It is the contents of the PC that are placed on the address bus to find and fetch the desired instruction. Since the PC is 16-bit width ,8051 can access program addresses from 0000H to FFFFH, a total of 6kB of code.

Stack Pointer Register (SP) : It is an 8-bit register which stores the address of the stack top. i.e the Stack Pointer is used to indicate where the next value to be removed from the stack should be taken from. When a value is pushed onto the stack, the 8051 first increments the value of SP and then stores the value at the resulting memory location. Similarly, when a value is popped off the stack, the 8051 returns the value from the memory location indicated by SP, and then decrements the value of SP. Since the SP is only 8-bit wide it is incremented or decremented by two. SP is modified directly by the 8051 by six instructions: PUSH, POP, ACALL, LCALL, RET, and RETI. It is also used intrinsically whenever an interrupt is triggered.

#### STACK in 8051 Microcontroller:

The stack is a part of RAM used by the CPU to store information temporarily. This information may be either data or an address. The CPU needs this storage area as there are only limited number of registers. The register used to access the stack is called the Stack pointer which is an 8-bit register. So, it can take values of 00 to FF When the8051 is powered up, the SP register contains the value 07.i.e the RAM location value 08 is the first location being used for the stack by the 8051 controller

There are two important instructions to handle this stack.One is the PUSH and the Other is the POP. The loading of data from CPU registers to the stack is done by PUSH and the loading of the contents of the stack back into aCPU register is done by POP.

EX: MOV R6 ,#35 H MOV R1 ,#21 H PUSH 6 PUSH 1

In the above instructions the contents of the Registers R6 and R1 are moved to stack and they occupy the 08 and 09 locations of the stack. Now the contents of the SP are incremented by two and it is 0A

Similarly, POP 3 instruction pops the contents of stack into R3 register. Now the contents of the SP is decremented by 1

In 8051 the RAM locations 08 to 1F (24 bytes) can be used for the Stack.In any program if we need more than 24 bytes of stack ,we can change the SP point to RAM locations 30-7F H.this can be done with the instruction MOV SP,# XX.

#### **Data Pointer Register(DPTR):**

It is a 16-bit register which is the only user-accessible. DPTR, as the name suggests, is used to point to data. It is used by a number of commands which allow the 8051 to access external memory. When the 8051 accesses external memory it will access external memory at the address indicated by DPTR. This DPTR can also be used as two 8-registers DPH and DPL.

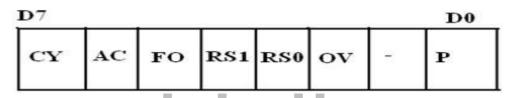

#### **Program Status Register (PSW):**

The 8051 has a 8-bit PSW register which is also known as Flag register. In the 8bit register only 6-bits are used by 8051. The two unused bits are user definable bits. In the 6-bits four of them are conditional flags. They are Carry –CY, Auxiliary Carry-AC, Parity-P, and Overflow-OV. These flag bits indicate some conditions that resulted after an instruction was executed.

# Figure 3.1.2 Program Status Word of 8051 Microcontroller

[Source: "Microprocessor Architecture Programming and Application" by R.S. Gaonkar, page- ]

The bits PSW3 and PSW4 are denoted as RS0 and RS1 and these bits are used th select the bank registers of the RAM location. The meaning of various bits of PSW register is shown below.

| CY  | PSW.7 | Carry Flag                            |

|-----|-------|---------------------------------------|

| AC  | PSW.6 | Auxiliary Carry Flag                  |

| FO  | PSW.5 | Flag 0 available for general purpose. |

| RS1 | PSW.4 | Register Bank select bit 1            |

| RS0 | PSW.3 | Register bank select bit 0            |

| OV  | PSW.2 | Overflow flag                         |

|     | PSW.1 | User difinable flag                   |

| Р   | PSW.0 | Parity flag .set/cleared by hardware. |

www.binils.com for Anna University | Polytechnic and Schools

The selection of the register Banks and their addresses are given below.

| RS1 | RS0 | Register Bank | Address |

|-----|-----|---------------|---------|

| 0   | 0   | 0             | 00H-07H |

| 0   | 1   | 1             | 08H-0FH |

| 1   | 0   | 2             | 10H-17H |

| 1   | 1   | 3             | 18H-1FH |

# www.binils.com

Download Binils Android App in Playstore

Download Photoplex App

# **3.4 I/O PORTS AND DATA TRANSFER CONCEPTS**

### Parallel I /O Ports :

The 8051 microcontroller has four parallel I/O ports , each of 8-bits .So, it provides the user 32 I/O lines for connecting the microcontroller to the peripherals. The four ports are P0 (Port 0), P1(Port1) ,P2(Port 2) and P3 (Port3). Upon reset all the ports are output ports. In order to make them input, all the ports must be set i.e a high bit must be sent to all the port pins. This is normally done by the instruction "SETB".

Ex: MOV A,#0FFH ; A = FF MOV P0,A ; make P0 an input port

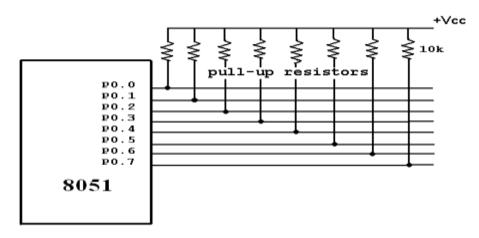

#### PORT 0:

Port 0 is an 8-bit I/O port with dual purpose. If external memory is used, these port pins are used for the lower address byte address/data (AD0-AD7), otherwise all bits of the port are either input or output.. Unlike other ports, Port 0 is not provided with pull-up resistors internally ,so for PORT0 pull-up resistors of nearly 10k are to be connected externally as shown.

#### Dual role of port 0:

Port 0 can also be used as address/data bus(AD0-AD7), allowing it to be used for both address and data. When connecting the 8051 to an external memory, port 0 provides both address and data. The 8051 multiplexes address and data through port 0 to save the pins. ALE indicates whether P0 has address or data. When ALE = 0, it provides data D0-D7, and when ALE =1 it provides address and data with the help of a 74LS373 latch.

#### Figure 3.4.1 Dual role of port 0

[Source: "Microprocessor Architecture Programming and Application" by R.S. Gaonkar, page-]

#### Port 1:

Port 1 occupies a total of 8 pins (pins 1 through 8). It has no dual application and acts only as input or output port. In contrast to port 0, this port does not need any pull-up resistors since pull-up resistors connected internally. Upon reset, Port 1 is configured as an output port. To configure it as an input port, port bits must be set i.e a high bit must be sent to all the port pins. This is normally done by the instruction "SETB".

Ex: MOV A, #0FFH; A=FF HEX

MOV P1, A; make P1 an input port by writing 1's to all of its pins

# Port 2:

Port 2 is also an eight-bit parallel port. (pins 21- 28). It can be used as input or output port. As this port is provided with internal pull-up resistors it does not need any external pull-up resistors. Upon reset, Port 2 is configured as an output port. If the port is to be used as input port, all the port bits must be made high by sending FF to the port. For

Ex:MOV A, #0FFH; A=FF hexMOV P2, A; make P2 an input port by writing all 1's to it

# **Dual role of port 2:**

Port2 lines are also associated with the higher order address lines A8-A15. In systems based on the 8751, 8951, and DS5000, Port2 is used as simple I/O port. But, in 8031-based systems, port 2 is used along with P0 to provide the 16-bit address for the external memory. Since an 8031 is capable of accessing 64K bytes of external memory, it needs a path for the 16 bits of the address. While P0 provides the lower 8 bits via A0-A7, it is the job of P2 to provide bits A8-A15 of the address. In other words, when 8031 is connected to external memory, Port 2 is used for the upper 8 bits of the 16-bit address, and it cannot be used for I/O operations.

# PORT 3:

Port3 is also an 8-bit parallel port with dual function. (pins 10 to 17). The port pins can be used for I/O operations as well as for control operations. The details of these additional operations are given below in the table. Port 3 also do not need any external pull-up resistors as they are provided internally similar to the case of Port2 & Port 1. Upon reset port 3 is configured as an output port. If the port is to be used as input port, all the port bits must be made high by sending FF to the port.

**Port 1E**x: MOV A, #0FFH ; A= FF hex

Port 1 occupitesQMdRal, &f 8 pins (pinsnakteh Raugh Ba)put pastaby duaitingpatication cand Adteenates FinpettionsonfpHoptoH: In contrast to port 0, this port does not need any pull-up resistoR3s0naadpRB1-lupreesistabforethenRotEd(Receivel DattpomdeTextDR(TitahsisnicoDEEga)received anrounput quotionToigonEgaDitsiP2s2aaridpR3.ponte proceeduitformeestebre adeiniter auptighBitts rR0s4 backen f. foard ubechfor FinsefEh0saischbrandIP3 doared P3h7e arestreediton pissFiEB "the write and read signals of external memories connected in 8031 based systems

| S.No | Port 3 bit | Pin No | Function |  |

|------|------------|--------|----------|--|

| 1    | P3.0       | 10     | RxD      |  |

| 2    | P3.1       | 11     | TxD      |  |

| 3    | P3.2       | 12     | INTO     |  |

| 4    | P3.3       | 13     | INTI     |  |

| 5    | P3.4       | 14     | ТО       |  |

| 6    | P3.5       | 15     | T1       |  |

| 7    | P3.6       | 16     | WR       |  |

| 8    | P3.7       | 17     | RD       |  |

#### Serial communication

Serial communication uses only one or two data lines to transfer data and is generally used for long distance communication. In serial communication the data is sent as one bit at a time in a timed sequence on a single wire. Serial Communication takes place in two methods, Asynchronous data Transfer and Synchronous Data Transfer.

#### Asynchronous data transfer:

It allows data to be transmitted without the sender having to send a clock signal to the receiver. Instead, special bits will be added to each word in order to synchronize the sending and receiving of the data. When a word is given to the UART for Asynchronous transmissions, a bit called the "Start Bit" is added to the beginning of each word that is to be transmitted. The Start Bit is used to alert the receiver that a word of data is about to be sent, and to force the clock in the receiver into synchronization with the clock in the transmitter. Port 1After the Start Bit, the individual bits of the word of data are sent. Here each bit in the woPoirs transmitted afootex and By phases (prices almont of the bit and the bit of the bi

Baud rate is a measurement of transmission speed in asynchronous communication, it represents the number of bits/sec that are actually being sent over the serial link. The Baud count includes the overhead bits Start, Stop and Parity that are generated by the sending UART and removed by the receiving UART.

#### Synchronous data transfer:

In this method the receiver knows when to "read" the next bit coming from the sender. This is achieved by sharing a clock between sender and receiver. In most forms of serial Synchronous communication, if there is no data available at a given time to transmit, a fill character will be sent instead so that data is always being transmitted. Synchronous communication is usually more efficient because only data bits are transmitted between sender and receiver, however it will be costlier because extra wiring and control circuits are required to share a clock signal between the sender and receiver. Devices that use serial cables for their communication are split into two categories.

- 1. DTE (Data Terminal Equipment). Examples of DTE are computers, printers & terminals.

- 2. DCE (Data Communication Equipment). Example of DCE is modems.

#### **Parallel Data Transfer:**

Parallel communication uses multiple wires (bus) running parallel to each other, and can transmit data on all the wires simultaneously. i.e all the bits of the byte are transmitted at a time. So, speed of the parallel data transfer is extremely high compared to serial data transfer. An 8-bit parallel data transfer is 8-times faster than serial data transfer. Hence with in the computer all data transfer is mainly based on Parallel data transfer. But only limitation is due to the high cost, this method is limited to only short distance communications.

| Po  | r <b>§.N</b> o        | Serial Communication                                                                                                                        | Parallel Communication                                                                                                                                |

|-----|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 1 Por                 | t Datagy pian so total of i 8 april of the optimit lith                                                                                     | rDusch i8)truthansi modulah umphicatisty and                                                                                                          |

| act | s only                | as single lineatput port. In contrast to po                                                                                                 | ortho, us group of lines (Bus) any pull-u                                                                                                             |

| res | i <del>st</del> ors s | iRetpannerstionstokeenlaceted intern                                                                                                        | ally. Dethicese, spion 1 is configured a                                                                                                              |

| an  | output                | poor Freshtignsmission input port,                                                                                                          | pHighispendstrates saistion high bit mus                                                                                                              |

| be  | s <b>4</b> nt to      | alhthe poert piton Thise is at times ly done<br>an easy task.                                                                               | Partite Instruction in SETBre easily implemented in hardware                                                                                          |

|     | 5.                    | In terms of transmission channel<br>costs such as data bus cable length,<br>data bus buffers, interface<br>connectors, it is less expensive | It is more expensive                                                                                                                                  |

|     | 6                     | No, crosstalk problem                                                                                                                       | Crosstalk creates interference between the parallel lines.                                                                                            |

|     | 7                     | No effect of inter symbol interference and noise                                                                                            | Parallel ports suffer extremely from<br>inter-symbol interference (ISI) and<br>noise, and therefore the data can be<br>corrupted over long distances. |

| V   | 8                     | The bandwidth of serial wires is much higher.                                                                                               | The bandwidth of parallel wires is much lower.                                                                                                        |

|     | 9                     | Serial interface is more flexible to<br>upgrade, without changing the<br>hardware                                                           |                                                                                                                                                       |

|     | 10                    | Serial communication work effectively even at high frequencies.                                                                             | Parallel buses are hard to run at high frequencies.                                                                                                   |

#### **P.5**rInterrupts

Aortiiltexcuppies antexateorial pinisiteinsall theortigha@)dikthalssnthelural cappbicatiolleand inclouon lyt ashint part device pue epdet it is services to the poprograms publiclocis rass neise tech wyith the instistory signal public pressister is a service to drinte (HSR) of poprograms the Budlet. is ponfigured and the cimput upon signal configure is a stand leep uf iposh, pontebitis neuroscipan of SinTeBrupt Starts to execute the interrupt service routine until RETI (return from interrupt) Upon executing the RETI the microcontroller returns to the place where it was interrupted. Get pop PC from stack.

The 8051 microcontroller has FIVE interrupts in addition to Reset. They are

- Timer 0 overflow Interrupt

- Timer 1 overflow Interrupt

- External Interrupt 0(INT0)

- External Interrupt 1(INT1)

- Serial Port events (buffer full, buffer empty, etc) Interrupt

Each interrupt has a specific place in code memory where program execution (interrupt service routine) begins.

| • | External | Interrupt 0 | : | 0003 H |

|---|----------|-------------|---|--------|

|   |          | 1           |   |        |

- Timer 0 overflow : 000B H

- External Interrupt 1 : 0013 H

- Timer 1 overflow : 001B H

- Serial Interrupt : 0023 H

Upon reset all Interrupts are disabled & do not respond to the Microcontroller. These interrupts must be enabled by software in order for the Microcontroller to respond to them. This is done by an 8-bit register called Interrupt Enable Register (IE).

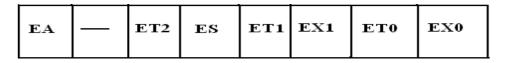

# **Interrupt Enable Register :**

**Port 1EA** : Global enable/disable. To enable the interrupts this bit must be set High.

• Port 1 Underfined-testel of 8 pirts (piesuse through 8). It has no dual application and acts on  $E_{T2}$ s: iEpuble /  $M_{S2}$  iEpuble /  $M_{S2}$  is presented and posterior presented in the port of the present of t

- ET0 : Enable /disable Timer 0 overflow interrupt.

- EX0 : Enable/disable External interrupt0

Upon reset the interrupts have the following priority.(Top to down). The interrupt with the highest PRIORITY gets serviced first.

- 1. External interrupt 0 (INT0)

- 2. Timer interrupt0 (TF0)

- 3. External interrupt 1 (INT1)

- 4. Timer interrupt1 (TF1)

5. Serial communication (RI+TI)

Priority can also be set to "high" or "low" by 8-bit IP register.- Interrupt priority register

|--|

IP.7: reserved

- IP.6: reserved

- IP.5: Timer 2 interrupt priority bit (8052 only)

- IP.4: Serial port interrupt priority bit

- IP.3: Timer 1 interrupt priority bit

- IP.2: External interrupt 1 priority bit

- IP.1: Timser 0 interrupt priority bit

- IP.0: External interrupt 0 priority bit

#### *BO***rME**MORY ORGANIZATION

MemoPyroilganiuptism total of 8 pins (pins 1 through 8). It has no dual application and acts on The Subplumic root putt polder. Hasch 20 stay tes of the Critical Span Adored 4kB not each any pRID Mp Reserve and the provest of the complete the second provide of the provide of

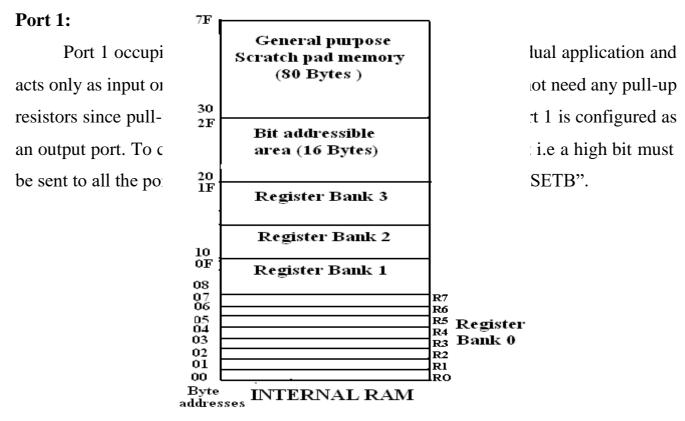

#### Internal RAM OF 8051 :

This Internal RAM is found on-chip on the 8051 .So it is the fastest RAM available, and it is also the most flexible in terms of reading, writing, and modifying it's contents. Internal RAM is volatile, so when the 8051 is reset this memory is cleared. The 128 bytes of internal RAM is organized as below.

(i) Four register banks (Bank0,Bank1, Bank2 and Bank3) each of 8-bits (total 32 bytes). The default bank register is Bank0. The remaining Banks are selected with the help of RS0 and RS1 bits of PSW Register.

(ii) 16 bytes of bit addressable area and

(iii) 80 bytes of general purpose area (Scratch pad memory) as shown in the diagram below. This area is also utilized by the microcontroller as a storage area for the operating stack.

The 32 bytes of RAM from address 00 H to 1FH are used as working registers organized as four banks of eight registers each. The registers are named as R0-R7 . Each register can be addressed by its name or by its RAM address.

EX : MOV A, R7 or MOV R7,#05H

Figure 3.3.1 Internal memory8051 Microcontroller

[Source: "Microprocessor Architecture Programming and Application" by R.S. Gaonkar, page-]

# Internal ROM (On -chip ROM):

The 8051 microcontroller has 4kB of on chip ROM but it can be extended up to 64kB.This ROM is also called program memory or code memory. The CODE segment is accessed using the program counter (PC) for opcode fetches and by DPTR for data. The external ROM is accessed when the EA(active low) pin is connected to ground or the contents of program counter exceeds 0FFFH.When the Internal ROM address is exceeded the 8051 automatically fetches the code bytes from the external program memory.

#### Figure 3.3.2 External memory8051 Microcontroller

[Source: "Microprocessor Architecture Programming and Application" by R.S. Gaonkar, page-]

#### **B**âr**PI**NOUTS

Port 806dcmpices constaller 8spinail(qbits als thr60ughn 8) IPt thip and that opplicate for other and the spinail of the spinail qbits als thr60ughn 8) IPt thip and the opplicate of the spinal of th

These two pins are connected to Quartz crystal oscillator which runs the on-chip oscillator. The quartz crystal oscillator is connected to the two pins along with a capacitor of 30pF as shown in the circuit. If we use a source other than the crystal oscillator, it will be connected to XTAL1 and XTAL2 is left unconnected.

# Figure 3.2.1 Pin Diagram of 8051 Microcontroller

[Source: "Microprocessor Architecture Programming and Application" by R.S. Gaonkar, page-]

#### **RST:**

The RESET pin is an input pin and it is an active high pin. When a high pulse is applied to this pin the microcontroller will reset and terminate all activities. Upon reset

all the registers except PC will reset to 0000 Value and PC register will reset to 0007 value.

#### EA (External Access):

This pin is an active low pin. This pin is connected to ground when microcontroller is accessing the program code stored in the external memory and connected to Vcc when it is accessing the program code in the on chip memory. This pin should not be left unconnected.

#### **PSEN (Program Store Enable) :**

This is an output pin which is active low. When the microcontroller is accessing the program code stored in the external ROM ,this pin is connected to the OE (Output Enable) pin of the ROM.

#### ALE (Address latch enable):

This is an output pin, which is active high. When connected to external memory, port 0 provides both address and data i.e address and data are multiplexed through port 0. This ALE pin will demultiplex the address and data bus .When the pin is High, the AD bus will act as address bus otherwise the AD bus will act as Data bus.

# P0.0- P0.7(AD0-AD7):

The port 0 pins multiplexed with Address/data pins .If the microcontroller is accessing external memory these pins will act as address/data pins otherwise they are used for Port 0 pins.

#### P2.0- P2.7(A8-A15) :

The port2 pins are multiplexed with the higher order address pins .When the microcontroller is accessing external memory these pins provide the higher order address byte otherwise they act as Port 2 pins.

#### P1.0- P1.7 :

These 8-pins are dedicated for Port1 to perform input or output port operations.

#### P3.0-P3.7:

These 8-pins are meant for Port3 operations and also for some control operations like Read,Write,Timer0,Timer1,INT0,INT1,RxD and TxD